#### ADDITIONAL MAXWELL MACMILLAN INTERNATIONAL EDITIONS IN COMPUTER SCIENCE

Adamson Antonakos Ellzey Hair Irvine Johnsonbaugh Khan Kroenke Leestma Loomis Mayer Nyhoff Ricardo Stallings Stallings

STRUCTURED C FOR TECHNOLOGY THE 68000 MICROPROCESSOR DATA STRUCTURES FOR COMPUTER INFORMATION SYSTEMS/2e MULTIVARIATE DATA ANALYSIS/2e ASSEMBLY LANGUAGE FOR THE IBM-PC APPLICATIONS PROGRAMMING IN C BEGINNING STRUCTURED COBOL DATABASE PROCESSING/3e PASCAL PROGRAMMING & PROBLEM SOLVING/3e THE DATABASE BOOK **PROGRAMMING IN MODULA-2** DATA STRUCTURES & PROGRAM DESIGN IN MODULA-2 DATABASE SYSTEMS: PRINCIPLES, DESIGN & IMPLEMENTATION COMPUTER ORGANIZATION & ARCHITECTURE/2e DATA & COMPUTER COMMUNICATIONS/2e ISDN: AN INTRODUCTION Stallings Stallings LOCAL NETWORKS/3e

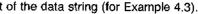

**INTRODUCTION TO COMPUTERS & INFORMATION** Szymanski SYSTEMS/2e

# 16/32-BIT MICROPROCESSORS 68000/68010/68020 Software, Hardware, and Design Applications

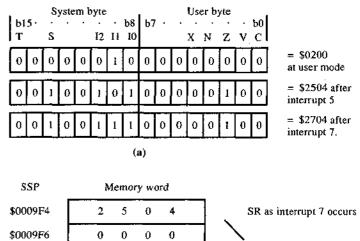

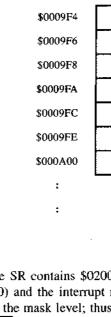

### PUTER SCIENCE COMPUTER SCIENCE COMPUTER SCIENCE COMPUTER SCIENCE COMPUTER SCIENCE COMPUTER SCIENCE COMP

MAXWELL MACMILLAN **INTERNATIONAL** EDITIONS

School Structure School School

**CESSO**

MAXWELL MACMILLAN INTERNATIONAL **EDITIONS**

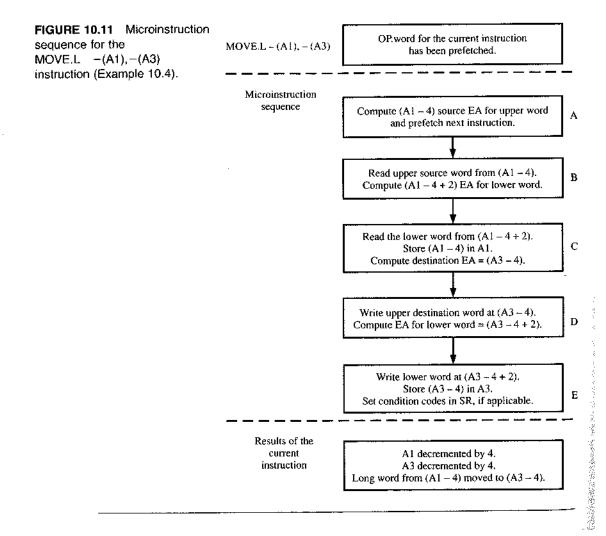

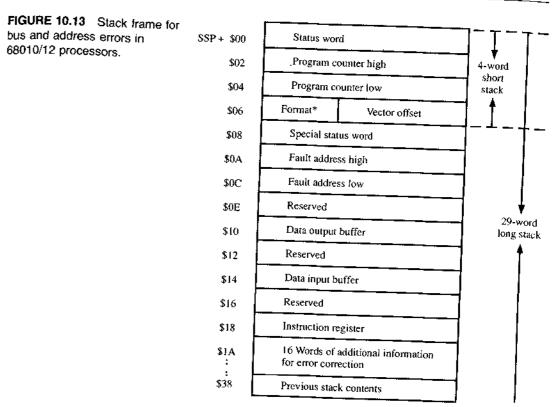

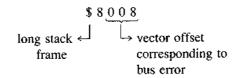

### PUTER SCIENCE COMPUTER SCIENCE COMPUTER SCIENCE COMPUTER SCIENCE COMPUTER SCIENCE COMPUTER SCIENCE COMP

ISBN 0-02-946331-9

WUNNAVA V. SUBBARAO

WUNNAVA V. SUBBARAO Florida International University

Merrill, an imprint of Macmillan Publishing Company New York

Collier Macmillan Canada, Inc. Toronto

Maxwell Macmillan International Publishing Group New York Oxford Singapore Sydney

# 16/32-Bit Microprocessors: 68000/68010/68020 Software, Hardware, and Design Applications

© Copyright 1991 by Macmillan Publishing Company. Merrill is an imprint of Macmillan Publishing Company.

Printed in the Republic of Singapore

All rights reserved. No part of this book may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or any information storage and retrieval system, without permission in writing from the publisher.

Distribution rights in this edition are controlled exclusively by Maxwell Macmillan Publishing Singapore Pte. Ltd. and restricted to selected countries. This book may be sold only in the country to which it has been sold or consigned by Maxwell Macmillan Publishing Singapore Pte. Ltd. Re-export to any other country is unauthorized and a violation of the rights of the copyright proprietor.

Macmillan Publishing Company 866 Third Avenue, New York, New York 10022

Collier Macmillan Canada, Inc.

Library of Congress Catalog Card Number: 90-60538

ISBN 0-675-21119-0 (Hardcover Edition) ISBN 0-02-946331-9 (International Edition)

IE Printing: 1 2 3 4 5 Year: 1 2 3 4 5

I2BN 0-05-84P337-8

To the respectful memory of my professors

Dr. Earnest Anderson, Ph.D., P.E., North Dakota State University, Fargo, and Dr. S. Jnanananda, Ph.D., D.Sc., Andhra University, Waltair, Andhra Pradesh, India. for their perseverance, compassion, and interest in my education,

and

I could venture and complete this project

To the Department of Electrical and Computer Engineering, Florida International University, Miami, for providing me with an outstanding professional atmosphere in which

In recent years, the single most important development in the field of digital electronics has been the microprocessor. Thanks to VLSI (very-large-scale integration), it has grown from the simple 4-bit processing element of a quarter-century ago to the complex 32/64-bit processing unit of the present time.

The Intel and Motorola corporations have been leaders in the development of microprocessors and associated electronic circuits. Currently, the two frontrunning families of microprocessors are the Intel 8086/186/286/386 family and the Motorola 68000/10/ 20/30 family. The Intel processors are very popular in such personal computers as the IBM PC and compatibles. The Motorola processors are equally popular in such personal computers as Apple's Macintosh, Commodore's Amiga, and Atari's ST. Most industrial controllers and systems, such as image-processing systems, robotic systems, and communication systems, are based on the Motorola 68000 family.

This book focuses on the Motorola family of microprocessors. It is written as a college-level text for electrical engineering and technology students, computer engineering and technology students, and computer science students. It can also serve as a self-teaching text for practicing engineering and technical personnel.

The book examines general software and hardware concepts of microprocessors, as well as microprocessor-based system design and implementation schemes, with specific reference to the 68000 family of processors. Descriptions of the software and hardware are sufficiently detailed to enable the reader to make use of the concepts in practical applications. Most of the software and hardware discussions are based on actual working models.

The 68000 family consists of the 16-bit 68000 processor, the 8-bit 68008 processor, the 16-bit virtual memory 68010 processor, the enhanced virtual memory 68012

## PREFACE

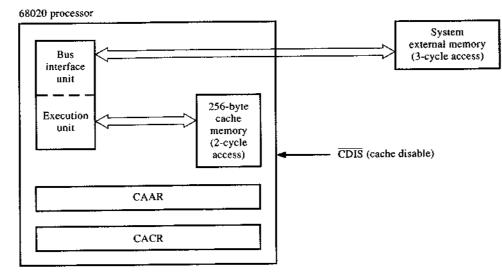

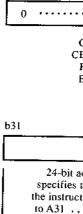

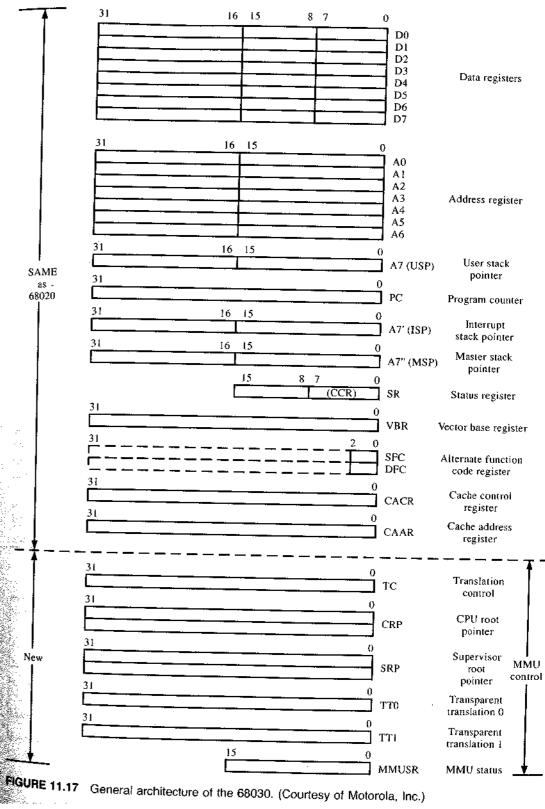

processor, the 32-bit cache memory 68020 processor, and the 32-bit enhanced cache memory 68030 processor. All of the later versions are based on the original 68000. Coverage of the text includes the architecture, software, hardware, and application details of the 68000 processor, with concepts extended to the other family members. Assembly programming techniques, parallel and serial I/O (input/output) interface techniques and associated applications, interrupt and DMA (direct memory access) applications, and system implementation schemes have been given particular emphasis.

**Chapter 1** presents the basic concepts of the 68000 family of microprocessors and introduces the architecture of the 68000. The special features of the 68000 family are also described. In **Chapter 2** the memory organization schemes, data structures, and addressing modes associated with the 68000 are covered, along with the instruction format and structure typical of the 68000 family. The instruction set of the 68000 is presented in **Chapter 3**, with particular emphasis on the general flow of the instruction structure, the instruction timing, and the instruction groups.

**Chapter 4** deals with software and programming techniques and applications of the 68000 processor. Assembly programming methods and special software features such as macros are examined in detail. The important aspect of exception processing is covered in **Chapter 5.** In this chapter, exception processing resulting from interrupts and error conditions is described.

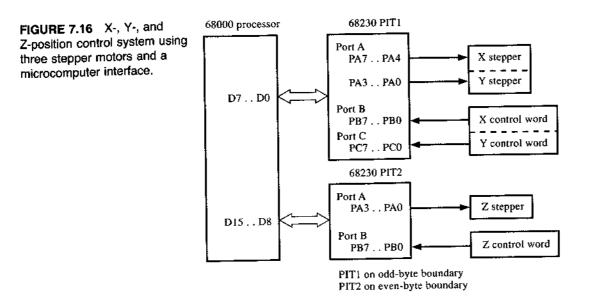

**Chapter** 6 deals with the hardware structure of the 68000 processor and the interfacing techniques with the memory and I/O. Important hardware concepts, such as address decoding, read and write bus cycle timing, and the VME and VERSA busing schemes, are introduced. This provides a foundation for the discussion on the parallel I/O interface to the 68000 and associated applications in **Chapter** 7. Important parallel interface devices, such as the 6821 PIA and 68230 PI/T, are introduced in this chapter. Data entry and display applications and position control using stepper motors are presented, along with hardware and software details. This leads to a description of the serial I/O interface to the 68000 and associated applications in **Chapter 8.** Industry standard serial interface devices, such as the 6850 ACIA and 68901 MFP, are introduced. RS-232 serial data communication and coded data transmission applications are presented, including hardware and software details.

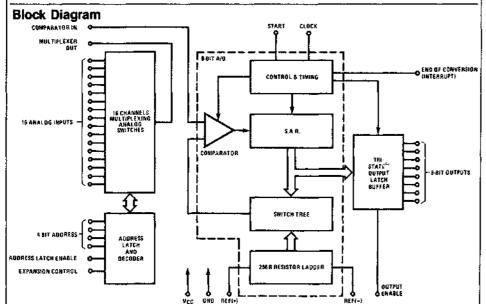

**Chapter** 9 deals with the most important aspects of the interrupts and the DMA (direct memory access) schemes associated with the 68000. Such practical applications as the daisy chain of interrupts, interrupt-driven gain controllers, and interrupt-driven data-acquisition systems with A/D and D/A are presented, again with hardware and software details. General concepts of the DMA are presented through a practical application using DMA-based high-speed data transfers.

**Chapter** 10 introduces the 68010 virtual memory processor. The general concepts of virtual memory, virtual machines, and the operating system are discussed in detail. The additional resources of the 68010 and 68012 processors are also covered, along with memory-access fault correction schemes using virtual memory concepts.

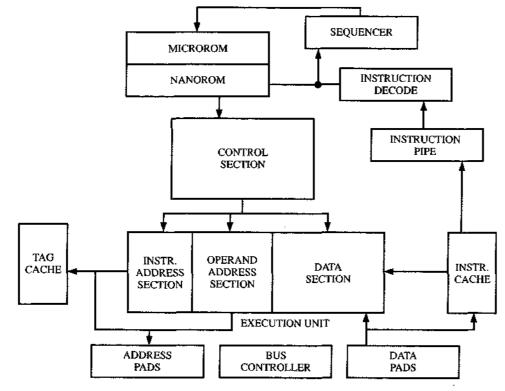

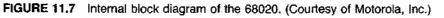

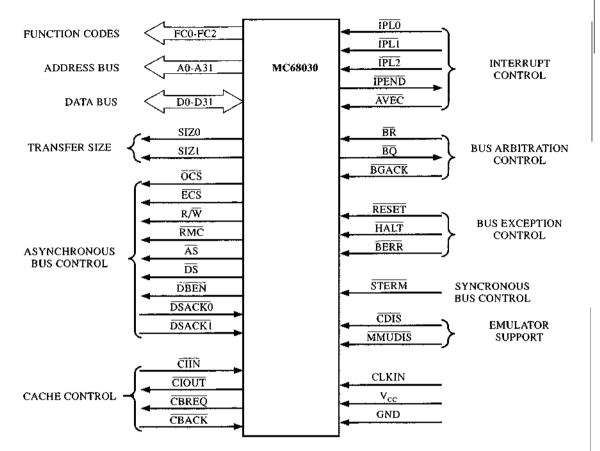

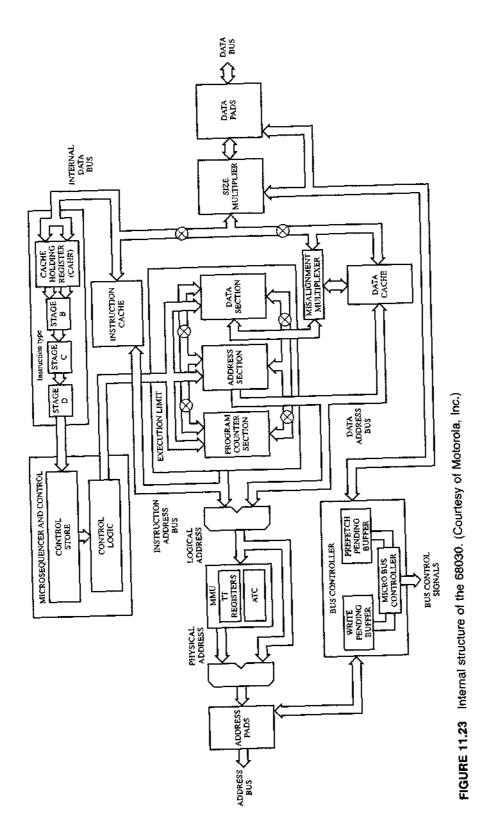

In **chapter** 11 the 32-bit 68020 and 68030 cache memory processors are introduced. The concepts of cache memory organization are discussed. Additional resources of the 68020 and 68030 processors and related performance improvements are presented. An objective comparison between the 68000 and the 68020/30 is also included to provide insight into the applications of these very powerful processors.

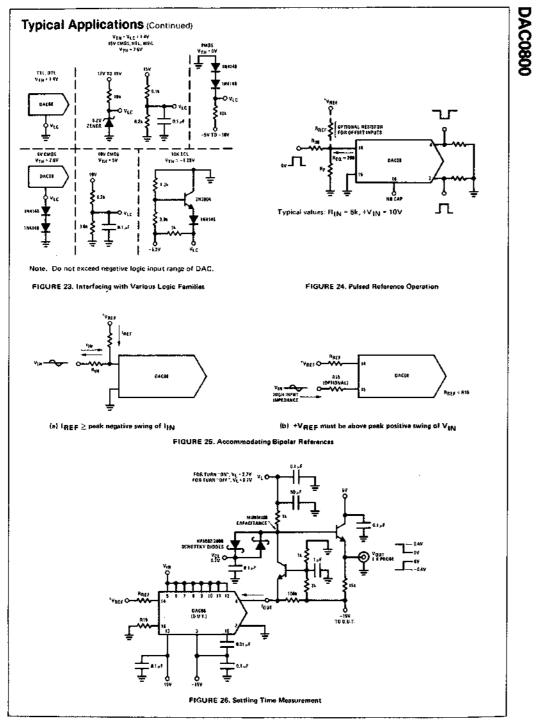

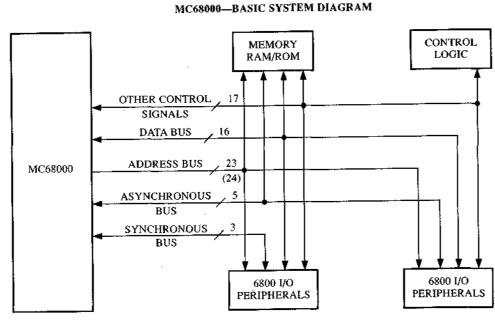

Finally, the book includes four appendices: Appendix A on number systems, Appendix B on the 68000 instruction set and condition uses, Appendix C on analog and digital converter devices for interfacing, and Appendix D on instruction timing for the 68000/10 processors.

The material is designed to be used in a two-semester course. For engineering and technical students, Chapters 1, 2, 3, 4, 5, and 6 can be covered in the first semester. In the second semester, Chapters 7, 8, 9, 10, and 11 can be covered. For computer science and software-oriented students, Chapters 1, 2, 3, 4, 5, and 10 can be covered in one semester. If instructors choose to introduce hardware before dealing with exceptions, they can switch the order of presentation of Chapters 5 and 6.

Each chapter is organized into four or five main sections, each dealing with an important topic. In most cases, each section has at least one example problem. The end-of-chapter problems are especially designed to supplement the material covered in the book. Most of these problems have been classroom tested. A comprehensive glossary is included at the end of the book.

The book is an outgrowth of several courses on microprocessors and digital systems taught by the author at Florida International University to engineering, technology. and computer science students. The author's association with the Motorola Corporation as a consulting professor, teaching their industrial seminars on the 68000 family of processors and applications, also significantly contributed to the book's development.

Nothing replaces a hands-on learning experience. Therefore, readers are encouraged to apply the software and hardware concepts introduced in this book to practical problems using the microcomputer system of their choice.

#### Acknowledgments

Many people assisted me in the preparation of this book. Students in the Electrical Engineering and Computer Science departments at Florida International University were extremely helpful. In particular, I would like to thank Jorge Salinger, Laura Ruiz, Mauracio Salinas, Fernando Gonzalez, and Mike Urucinitz of the Electrical Engineering Department for their work in conducting hardware and software experiments to support the discussions in this book.

Motorola Corporation has been very generous in donating 68000- and 68020-based systems to the university. This allowed for the concepts presented in the text to be tested on real systems. Special thanks to Ben Ledonne and Fritz Wilson of the university support service at the Motorola Corporation in Phoenix for their support and encouragement.

I would like to acknowledge the encouragement and guidance offered by our chairperson, James Story, and the professional courtesy extended to me by our dean. Gordon Hopkins, and associate dean, Manuel Cereijo, during the preparation of the book. Many thanks also to Lie Lonie Boney and Lordis Barough for their assistance in preparing the materials for presentation. I am especially grateful to my wife, Sunanda.

and to my children, Madhavi and Manoj, for their immense patience and understanding during the course of the project.

Perhaps no words can express my gratitude to my teachers. They have given me a path objective, a career, and, above all, knowledge and self-esteem. Professor Earnest Anderson and Professor Edwin Anderson of North Dakota State University in Fargo and Professor D.L. Sastry, the late Professor S. Jnanananda, and Professor D.S. Sastry of Andhra University in Waltair and Masulipatam in India have been instrumental in shaping my present academic career. I remain ever grateful to them. I would also like to thank the reviewers of this edition for their important ideas and suggestions: Antony Alumkal, Austin Community College; Mike Bachelder, South Dakota School of Mines and Technology; Gary Boyington, Chemeketa Community College; George Frueh, Lincoln Technical Institute; Frank Gergelyi, Metropolitan Technical Institute; Jerry Noe, Tri Cities State Technical School; and John Skroder, Texas A&M University.

#### INTRODUCTION

#### CHAPTER 1 The 68000 Family of Microprocessors and Architecture

### 1.0 INTRODUCTION 2

- 1.1 The 68000 FAMILY OF MICROPROCESSORS 2

- The 68000 Microprocessor 2

- The 68008 Microprocessor 2

- The 68010 Microprocessor 3

- The 68012 Microprocessor

- The 68020 Microprocessor 4

- The 68030 Microprocessor 4

- The 68881 Coprocessor

- 1.2 TYPICAL MICROCOMPUTER CONFIGURATION OF THE 68000 FAMILY 5 General Interface Scheme 5 Typical 68000-Based Systems 6

- 1.3 GENERAL ARCHITECTURE OF THE 68000 MICROPROCESSOR 7 Data Registers D0-D7 (Dn) 7 Address Registers A0-A6 (An) 8 Stack Pointers A7 (USP) and A7' (SSP) 8 Program Counter (PC) 9 Status Register (SR) and Flag Structure 9 Other Resources 12 Supervisor and User Modes of Operation

# CONTENTS

xix

1

13

xi

| 1.4        | OTHER FEATURES OF THE 68000 FAMILY OF PROCESSORS 15<br>Prefetch Queue 15<br>The Instruction Pipeline 15                                                                                                                                                                                                                                                           |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.5        | SUMMARY 15<br>PROBLEMS 16<br>ENDNOTES 18                                                                                                                                                                                                                                                                                                                          |

| The        | APTER 2<br>e 68000 Memory Organization Schemes, Data<br>uctures, and Addressing Modes                                                                                                                                                                                                                                                                             |

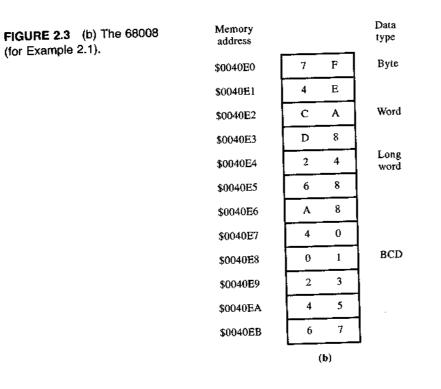

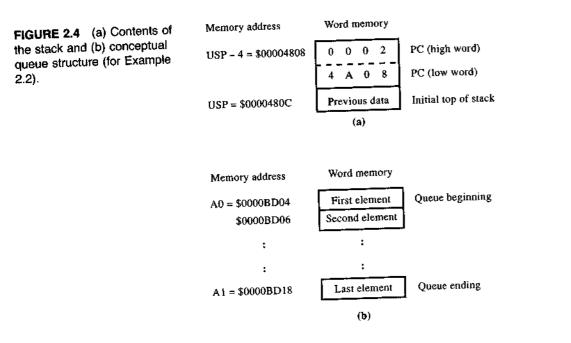

| 2.0<br>2.1 | INTRODUCTION20MEMORY ORGANIZATION SCHEMES AND DATA STRUCTURES20Memory Organization and Selection Schemes20Data Structures and Representation21Stack and Queue Organization and Structure for the 6800024                                                                                                                                                          |

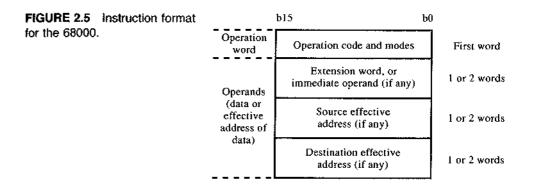

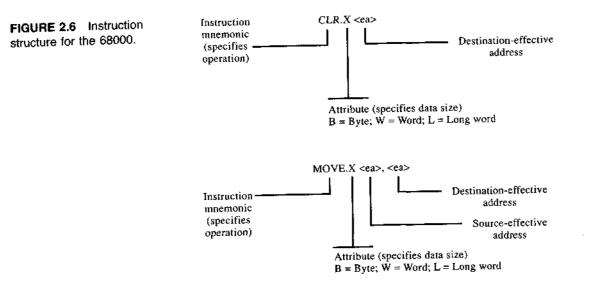

| 2.2        | INSTRUCTION FORMAT AND STRUCTURE26Instruction Format27Instruction Structure7                                                                                                                                                                                                                                                                                      |

| 2.3        | REGISTER DIRECT AND REGISTER INDIRECTADDRESSING MODES28 RegisterDirect Addressing Modes30 RegisterIndirect Addressing Modes30                                                                                                                                                                                                                                     |

| 2.4        | IMMEDIATE, QUICK, ABSOLUTE, RELATIVE,<br>AND IMPLICIT ADDRESSING MODES 34Immediate Addressing Mode (Imm) 35 QuickAddressing Mode (Q) 35Absolute Short and Long Addressing Modes (Abs.W, Abs.L) 36 PC Relative<br>with Displacement Addressing Mode d(PC) 37 PC Relative with Index and<br>Displacement Addressing Mode d(PC,Rn) 37 Implicit Addressing Mode<br>38 |

| 2.5        | SUMMARY 39<br>PROBLEMS 41<br>ENDNOTES 43                                                                                                                                                                                                                                                                                                                          |

| -          | APTER 3<br>68000 Instruction Set and Programming Considerations                                                                                                                                                                                                                                                                                                   |

| 3.0<br>3.1 | INTRODUCTION45THE GENERAL INSTRUCTION SET45Interpretation of the Instructions45The Instruction Groups50                                                                                                                                                                                                                                                           |

| 3.2        | DATA MOVEMENT AND ARITHMETIC INSTRUCTION GROUPS 52                                                                                                                                                                                                                                                                                                                |

- Data Movement Instructions 52

- Binary Integer Arithmetic Instructions 55 BCD

(Binary Coded Decimal) Instructions 62

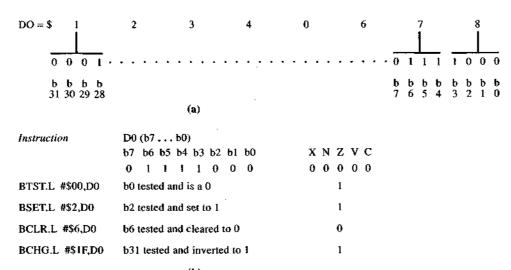

3.3 LOGICAL AND BIT-MANIPULATION Logic, Shift, and Rotate Instructions Bit-Manipulation Instructions 70

- 3.4 PROGRAM AND SYSTEM CONTROL INSTRUCTION GROUPS Program Control Instructions 73 System Control Instructions 76

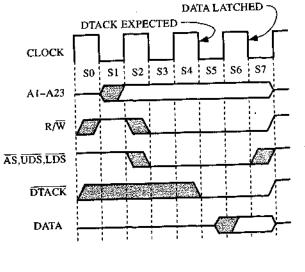

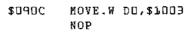

- 3.5 INSTRUCTION TIMING CONSIDERATIONS 78 Read/Write Timing 78 Instruction Timing Computation 78

- 3.6 SUMMARY 81 PROBLEMS 82 ENDNOTES 86

#### CHAPTER 4

19

44

68000 Software Considerations and Assembly Programming Applications

- 4.0 INTRODUCTION 88

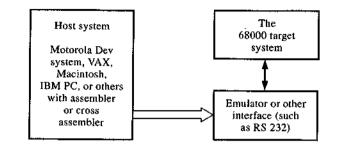

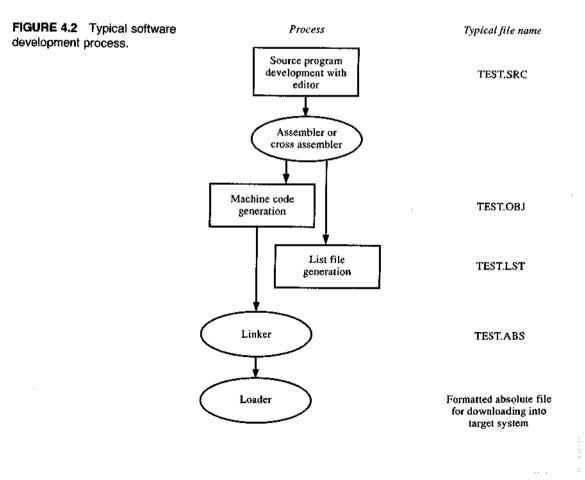

- 4.1 ASSEMBLY LANGUAGE SOFTWARE AND PROGRAMMING TECHNIQUES 88 Assembler, Cross Assembler, Linker, and Loader Utilities 88 Writing Assembly Programs and Software Development 90 Programming and Software Engineering Considerations 96

- 4.2 DATA MOVEMENT, DATA-COMPARISON SOFTWARE, AND APPLICATIONS Software Considerations Software Considerations 99

- 4.3 DATA PROCESSING APPLICATIONS AND SOFTWARE CONSIDERATIONS Subtraction Operations Operations 104

- 4.4 SPECIAL INSTRUCTION GROUPS AND APPLICATIONS Multiple-Decision Instructions 108 Address, Stack, and Multiple-Movement Instructions

- 4.5 MACROS IN SOFTWARE DEVELOPMENT

- 4.6 SUMMARY 117 PROBLEMS 118

- ENDNOTES 120

### CHAPTER 5

### 68000 Exception Processing Considerations

- 5.0 INTRODUCTION 122

- 5.1 GENERAL CONCEPTS OF EXCEPTION PROCESSING The Exception Vector Table and Exception Vectors

| N INSTRUCTION GROUPS | 64 |

|----------------------|----|

| 65                   |    |

73

96 Block Transfer Applications and 96 Data-Sequencing Applications and

101 Multiprecision Addition and 102 Multiplication and Division

#### 108

110 115

122 122

87

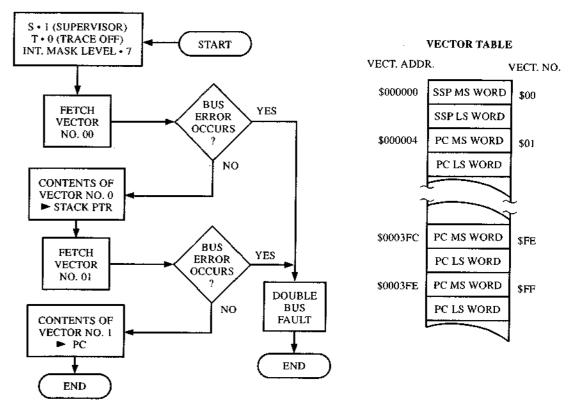

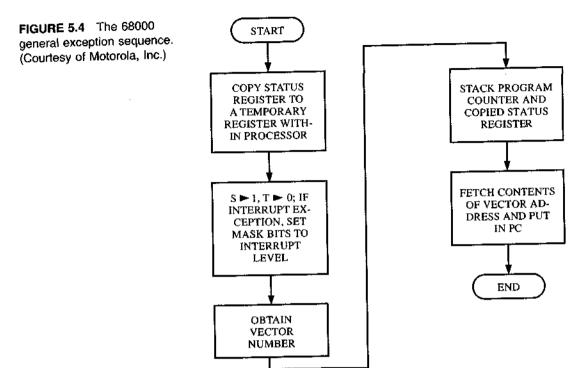

|            | Reset Exception Processing123General Scheme of Exception Processing125                                                                                                                                                                                                                   |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

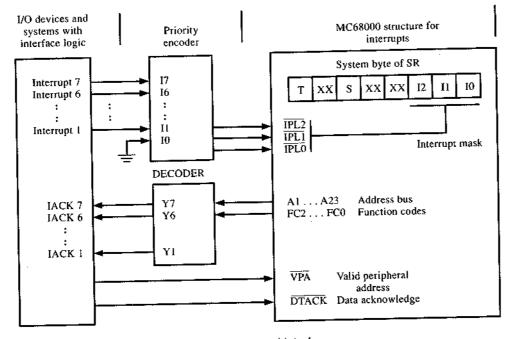

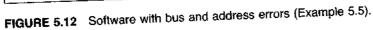

| 5.2        | INTERRUPT EXCEPTIONS AND APPLICATIONS128Interrupt Mask Levels128Autovector and User Vector Methods129                                                                                                                                                                                    |

| 5.3        | TRAP EXCEPTION PROCESSING AND APPLICATIONS132Using System Resources in the Supervisor Mode via Traps133Trap Software Routines and Applications133                                                                                                                                        |

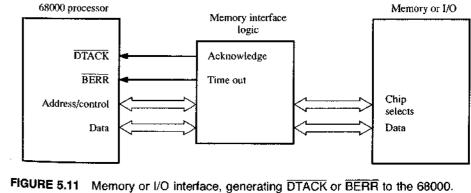

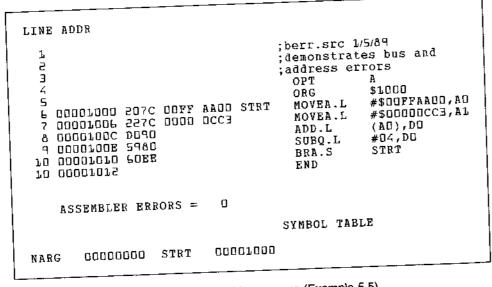

| 5.4        | ERROR-RELATED EXCEPTIONS135Illegal Instruction, Unimplemented Instruction,<br>and Privilege-Violation Conditions136Uninitialized and Spurious Interrupt Exceptions137Zero-divide, CHK, and Trace Exception Conditions137Address and Bus Error Conditions138Double Bus Fault Condition142 |

| 5.5        | SUMMARY 142<br>PROBLEMS 143<br>ENDNOTES 147                                                                                                                                                                                                                                              |

|            | APTER 6<br>000 Hardware Considerations and Design Applications                                                                                                                                                                                                                           |

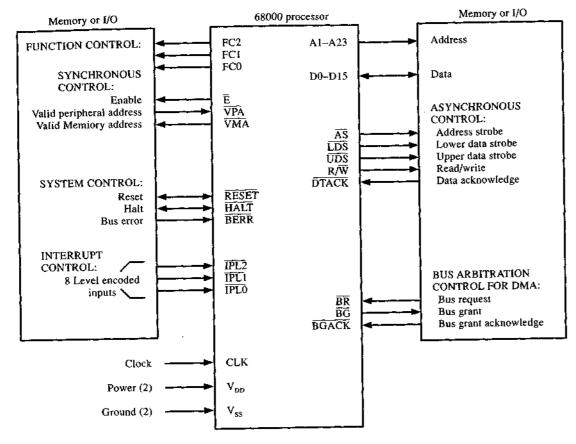

| 6.0<br>6.1 | INTRODUCTION14868000 HARDWARE SIGNALS AND FUNCTIONS149 Address,Data, and Asynchronous Buses for the 68000150 Function CodeOutputs151Other Buses and Signals152                                                                                                                           |

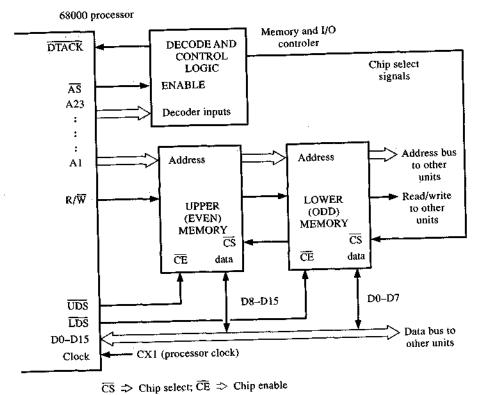

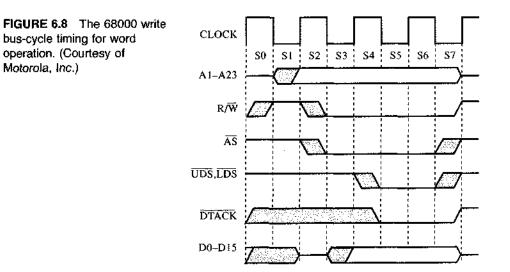

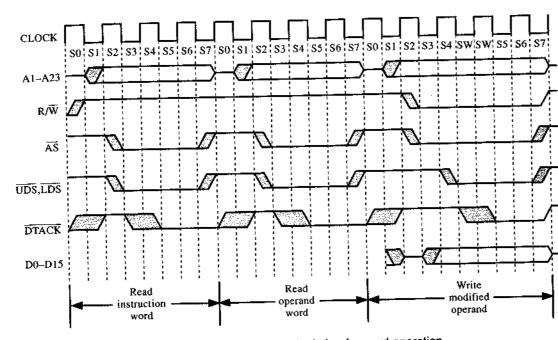

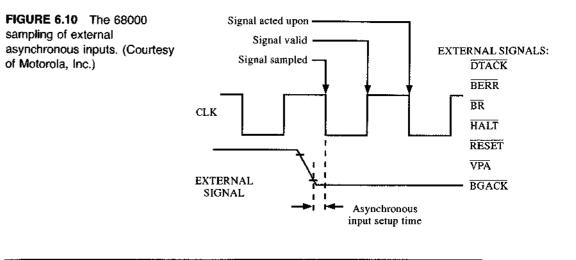

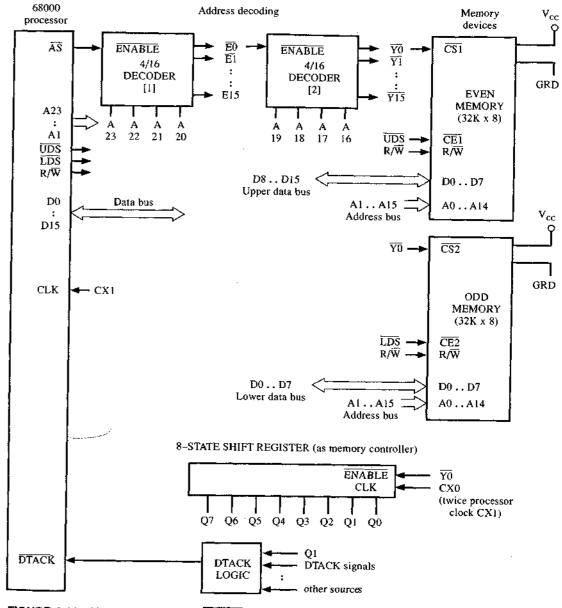

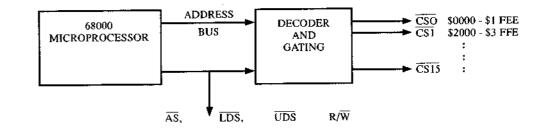

| 6.2        | MEMORY AND I/O INTERFACE SCHEMES156Memory-Device Types and Memory Concepts156Address Decoding, Strobing, and Memory Selection157Read and Write Timing Considerations157Timing Considerations of Asynchronous Inputs160                                                                   |

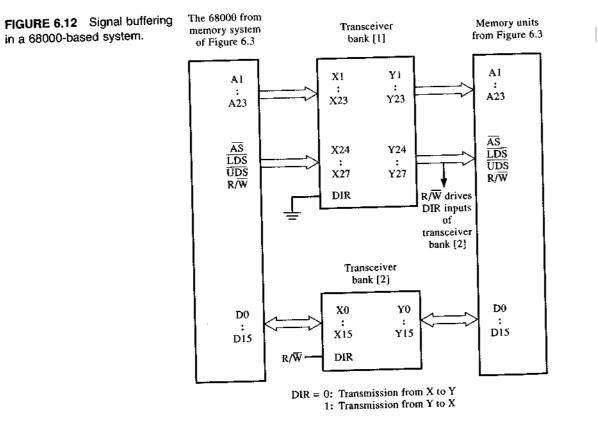

| 6.3        | MEMORY AND I/O SYSTEM DESIGN CONSIDERATIONS162The Memory Subsystem Design162Signal Buffering Considerations164                                                                                                                                                                           |

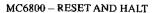

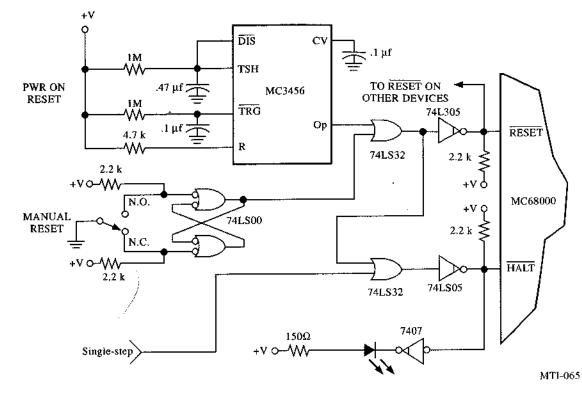

| 6.4        | CONTROL INTERFACE SCHEMES166Reset and Halt Interface166Timing Signals Associated with the 68000168Bus Error Considerations169                                                                                                                                                            |

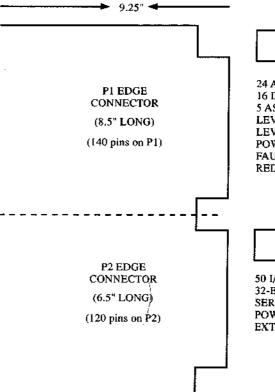

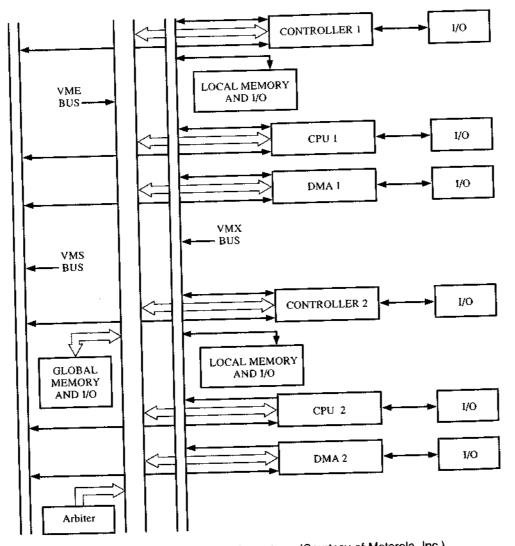

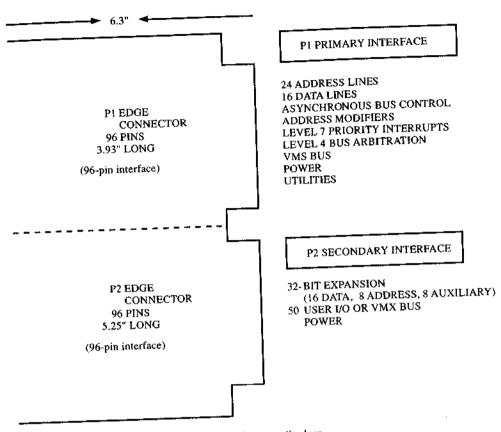

| 6.5        | 68000-BASED BUSING SCHEMES 170<br>The VERSA Bus 170<br>The VME Bus 173                                                                                                                                                                                                                   |

- 6.6 SUMMARY 176

- PROBLEMS 176

- ENDNOTES 179

### CHAPTER 7

#### The 68000 Parallel Interface and Applications

- 7.0 INTRODUCTION 180

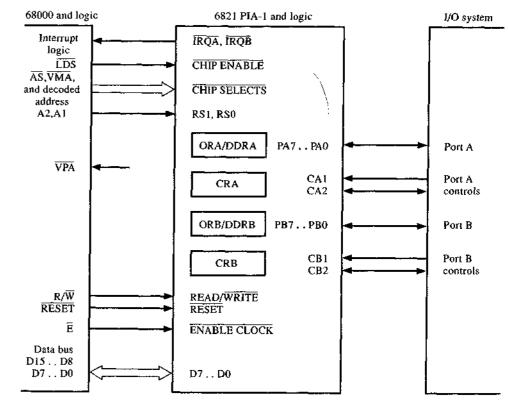

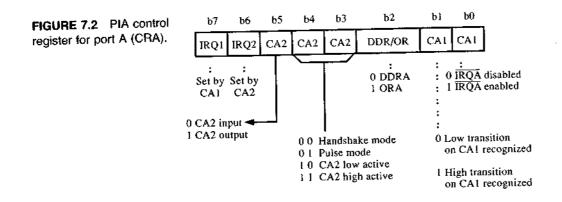

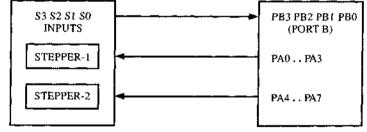

- 7.1 SYNCHRONOUS PARALLEL INTERFACE WITH THE 68000 6821 PIA (Peripheral Interface Adapter) Architecture 181 6821 PIA Synchronous Interface with the 68000 182 I/O Interface and Design Applications 183

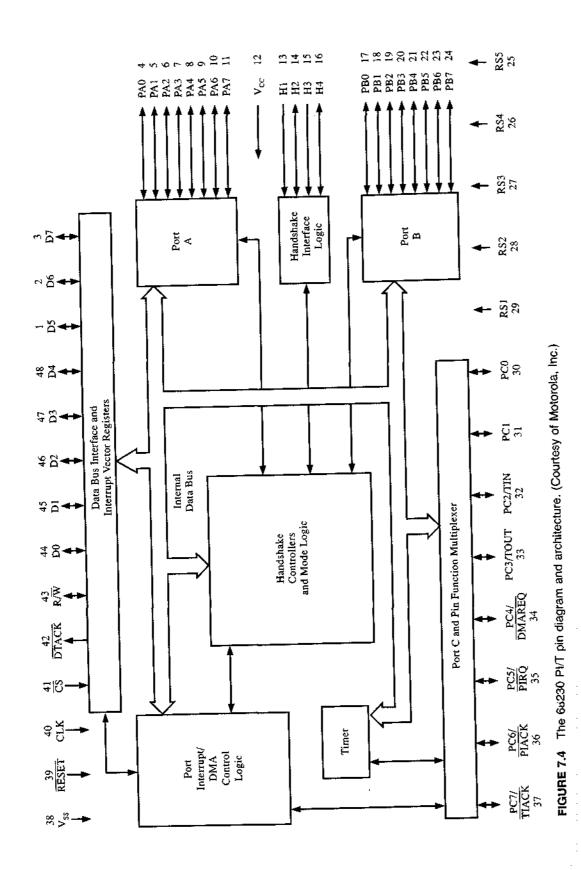

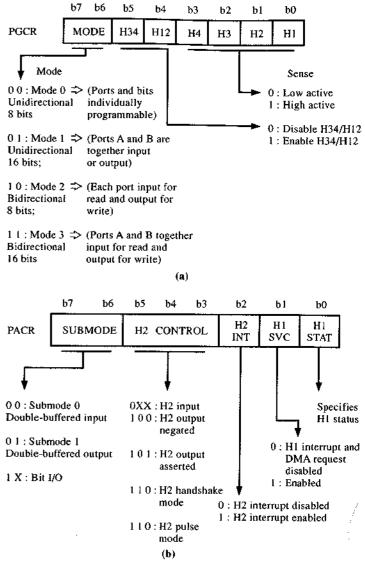

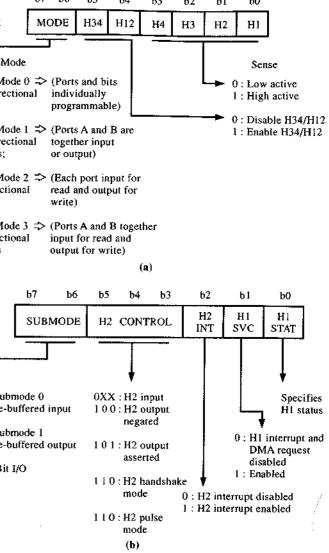

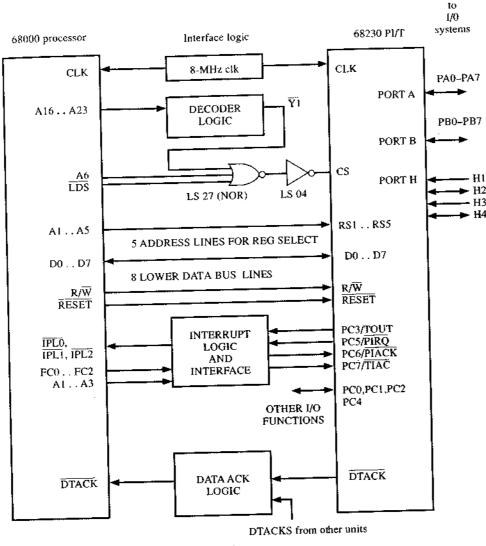

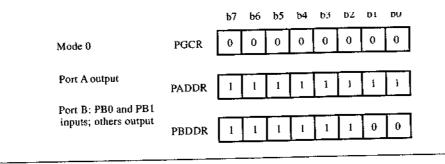

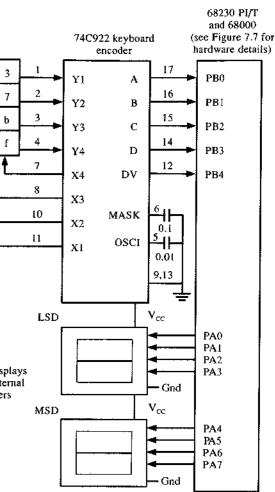

- 7.2 THE 68230 PARALLEL INTERFACE AND TIMER (PI/T) Registers and I/O Ports 187 Interfacing the 68230 PI/T 189

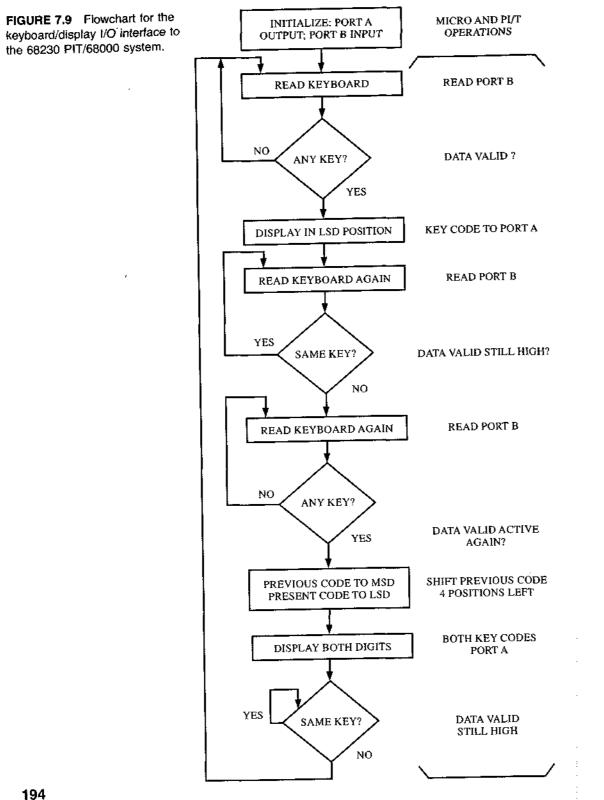

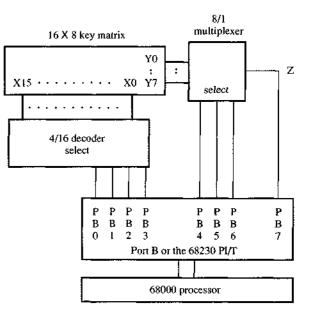

- 7.3 DATA ENTRY AND DISPLAY SYSTEMS Keyboard and Hex Display Interface 192 System Hardware and Software Considerations 192 Other Forms of Keyboard and Interface Schemes 197

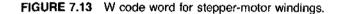

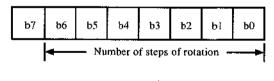

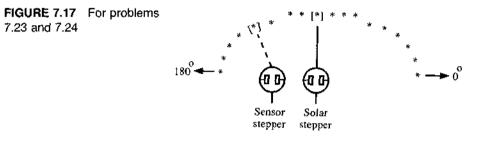

- 7.4 ELECTROMECHANICAL APPLICATIONS 198 Rotational and Linear Stepper Motors 199 Stepper-Motor Interface Considerations 199 Position Control Systems 203

- 7.5 SUMMARY 204 PROBLEMS 205 ENDNOTES 208

### CHAPTER 8

148

#### The 68000 Serial Interface and Applications

- 8.0 INTRODUCTION 209

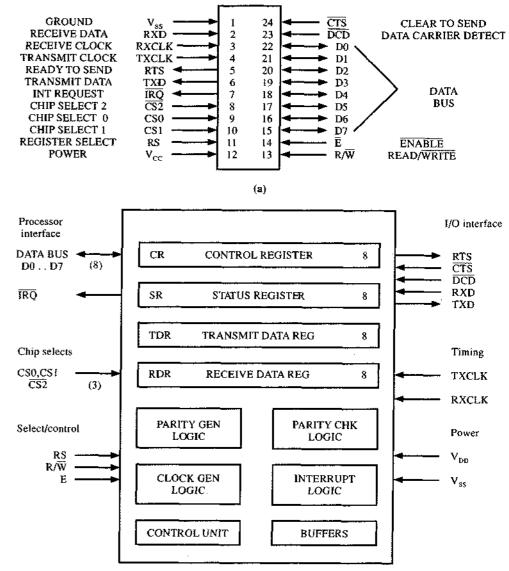

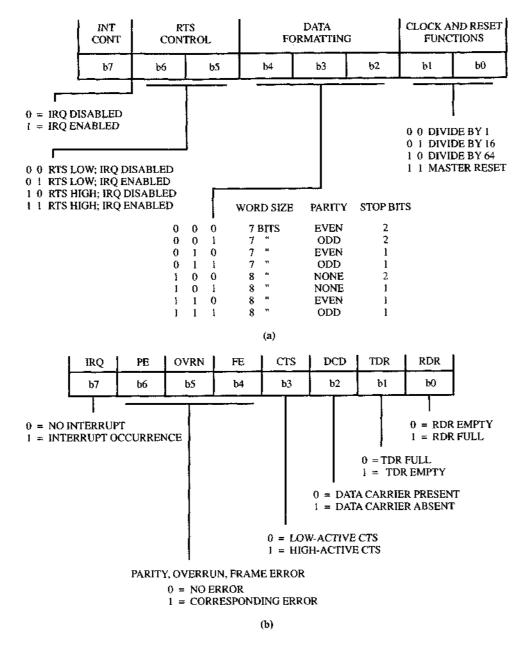

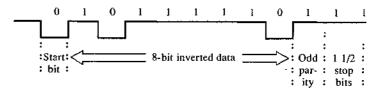

- 8.1 SERIAL DATA COMMUNICATION CONCEPTS 210 8.2 6850 ACIA GENERAL ARCHITECTURE 212 Registers and I/O Ports 212

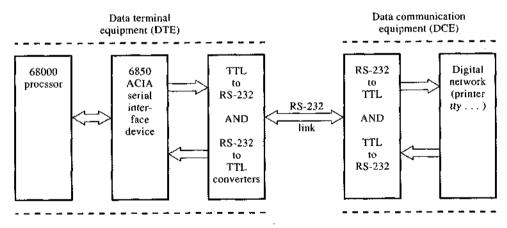

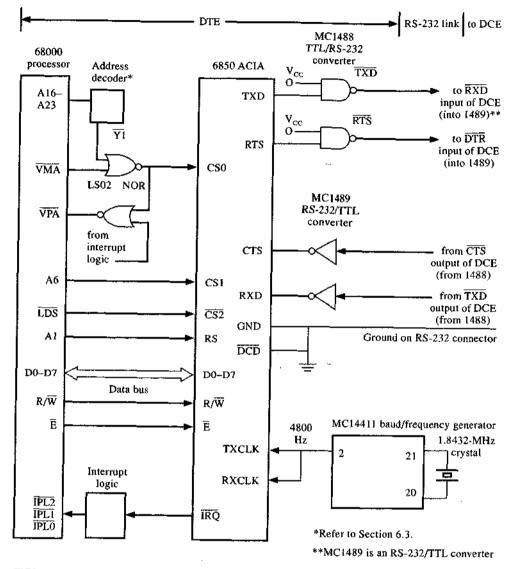

- 8.3 THE 6850 ACTA INTERFACE WITH THE 68000 AND APPLICATIONS 216 68000/6850 Interface Considerations 216 RS-232 Interface Application 218

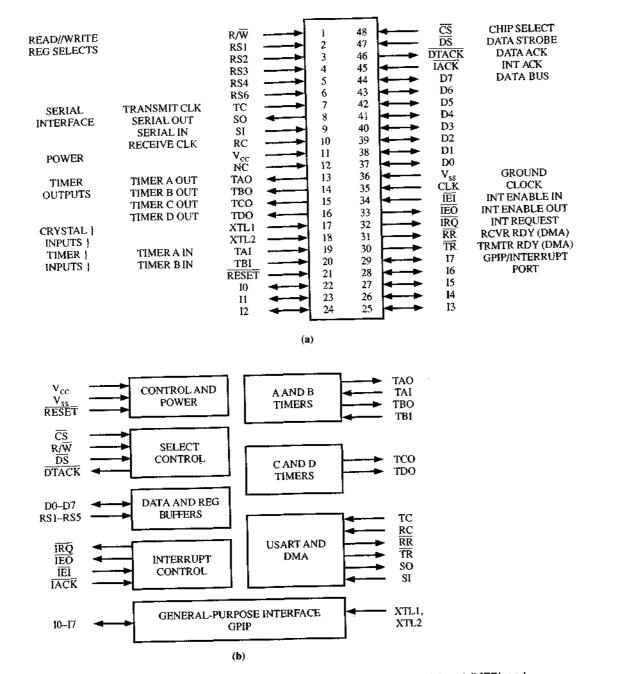

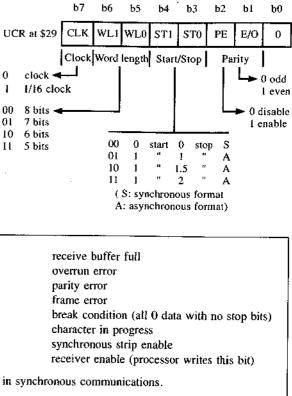

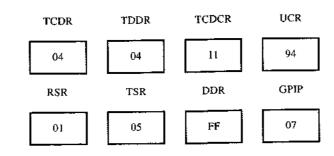

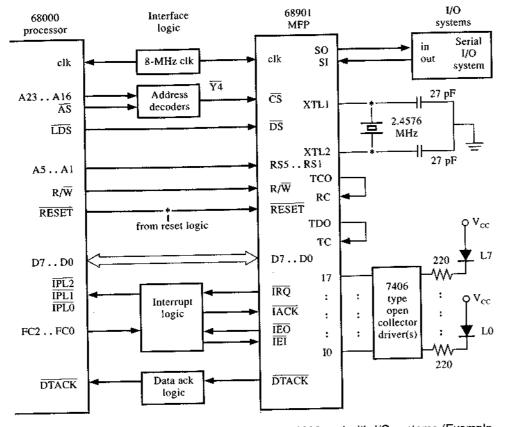

- 8.4 68901 MFP (MULTIFUNCTION PERIPHERAL) GENERAL ARCHITECTURE 220 Internal Architecture of the MFP 221 Register Structure and Modes of Operation 221

181 187

192 The

Modes of Operation and Status Conditions of the ACIA 213

180

| 68000                       | 1 MFP INTERFACE WITH THE 68000 AND APPLICATIONS2270/68901 and I/O Interface Considerations227ed Data Communication System228                                                         |     | <b>10.3</b> MEMORY FAULT CORRECTION SCI<br>The instruction Restart Method 290<br>The Instruction Continuation Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROF                        | IMARY 232<br>BLEMS 232<br>NOTES 234                                                                                                                                                  |     | The 68010/68012 Memory Fault Correc<br><b>10.4</b> BUS ERROR EXCEPTION PROCESS<br>WITH VIRTUAL MEMORY 293<br>Processing 293 Correction of Memory<br>Memory Schemes 297                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| The 6800                    | 00 Interrupt and DMA Interface and Applications                                                                                                                                      | 236 | 10.5 SUMMARY 301                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

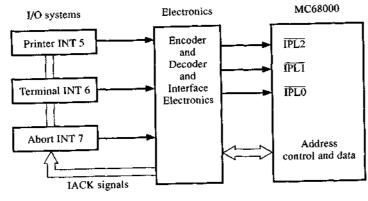

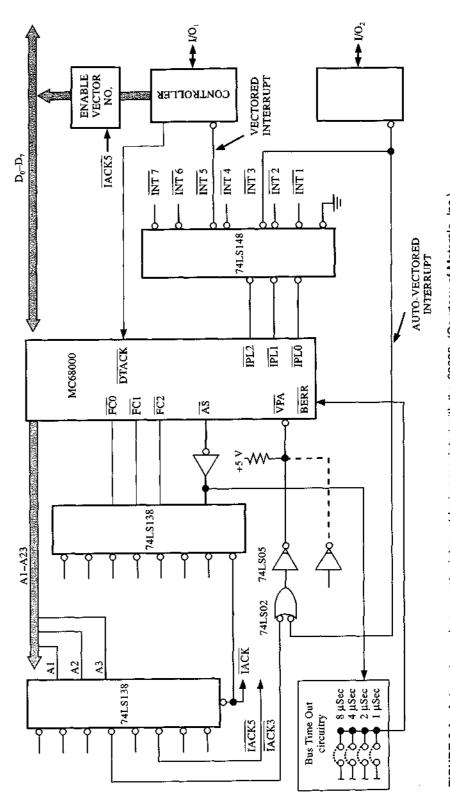

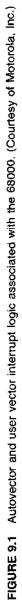

| 9.1 INTE<br>Autov<br>Interr | RODUCTION236ERRUPT INTERFACE CONSIDERATIONS238ovectored and User-Vectored Interrupt Logic238rupt Controllers239rupt Expansion and the Daisy-Chain Mechanism240                       |     | PROBLEMS 302<br>ENDNOTES 305<br>CHAPTER 11<br>68020 and 68030 Architecture, Organ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

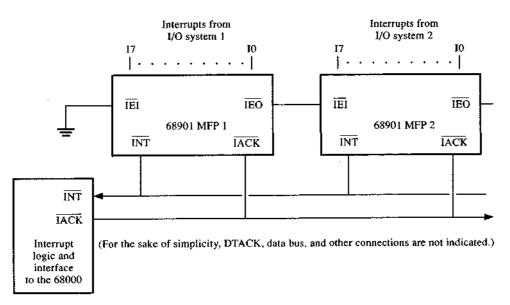

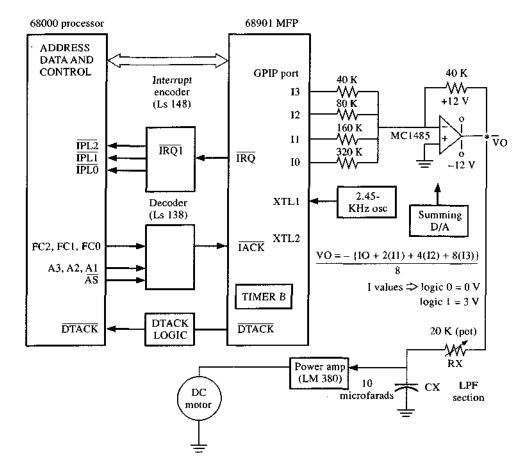

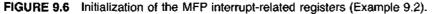

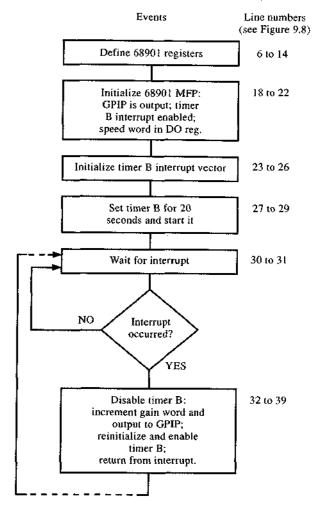

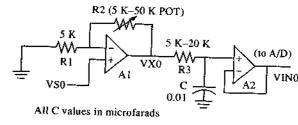

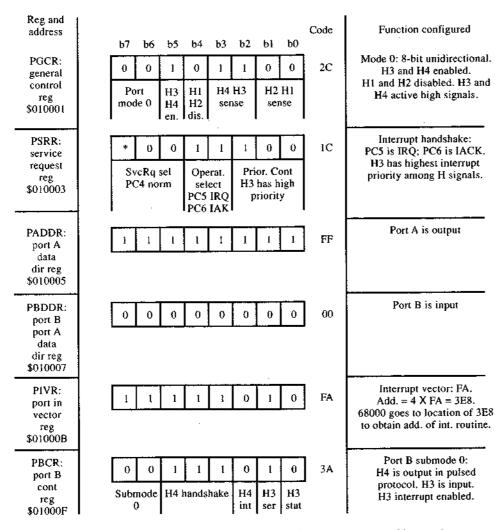

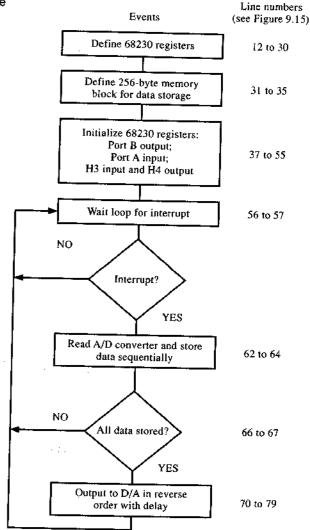

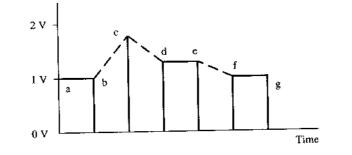

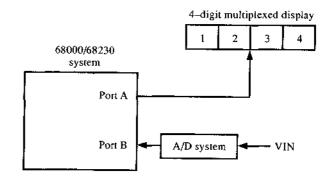

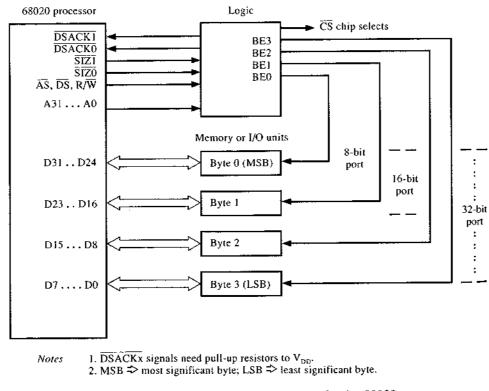

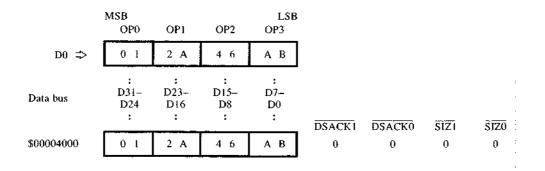

| 9.2 INTE<br>Interr          | rupt Expansion and the Daisy-Chain Mechanism240ERRUPT-DRIVEN SYSTEM APPLICATIONS242rupt-Driven Gain Controller242amic Random Access Memory (DRAM) Interface247                       |     | <ul><li>11.0 INTRODUCTION 306</li><li>11.1 GENERAL ARCHITECTURE OF THE Resources and Modified Resources of the sources of the</li></ul> |

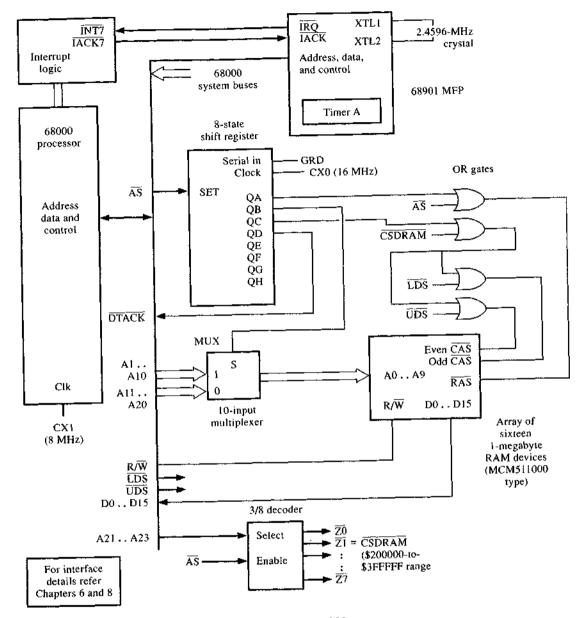

| SY                          | INTERRUPT-DRIVEN DATA-ACQUISITION<br>YSTEM AND APPLICATIONS 253                                                                                                                      |     | Data, and Control Buses 309<br>Data Formats, Memory, and I/O Interfac<br><b>11.2</b> ADDITIONAL ADDRESSING MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

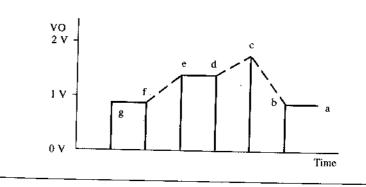

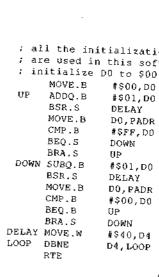

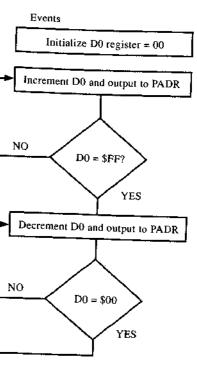

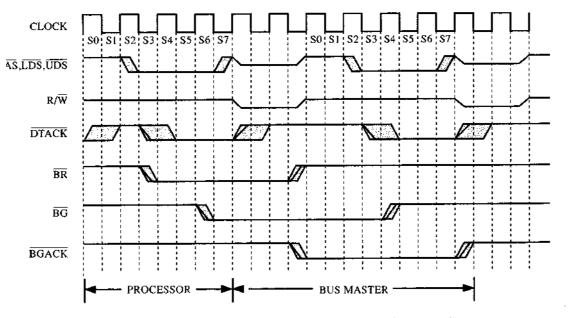

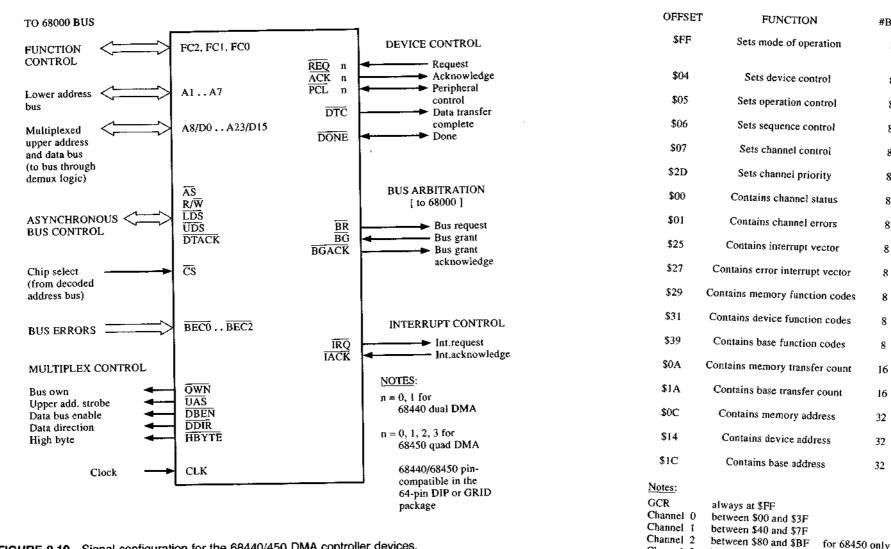

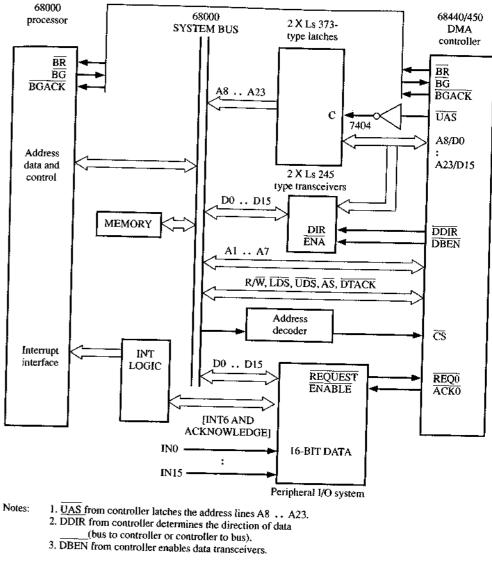

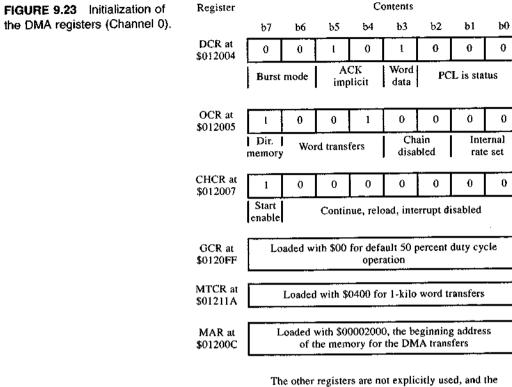

| Data-<br>9.4 DIRE<br>Gener  | A/D and D/A Interface253 A Typical-Acquisition System258ECT MEMORY ACCESS (DMA) CONSIDERATIONS260eral Architecture of the DMA Controllers26068440 and 68450 DMA Controllers263 Modes |     | FOR THE 68020 313 Memory Ind<br>Modes and Scaling 313 Bit-Field Ty<br>314 Packed and Unpacked BCD Instruct<br>Instructions and Enhancements 320                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| of Op<br>9.5 THE            | peration of the DMA Controllers 263<br>DMA INTERFACE AND APPLICATIONS 266                                                                                                            |     | <b>11.3</b> CACHE MEMORY CONCEPTS AND<br>68020 Cache Memory Organization and<br>Control and Cache Address Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DMA                         | A Sequence of Operations267A Channel Initialization269A Software Considerations270                                                                                                   |     | 11.4 GENERAL ARCHITECTURE OF THE<br>Instruction and Data Cache Memory Org                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PROI                        | IMARY 272<br>BLEMS 274<br>NOTES 276                                                                                                                                                  |     | Additional Software Resources of the 68<br>Additional Hardware Resources of the 6<br><b>11.5</b> FUNCTIONAL IMPROVEMENTS OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CHAPTE                      | R 10                                                                                                                                                                                 | 070 | AND 68030 PROCESSORS 331<br>Capability 331 32-Bit Extended Inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                             | nd 68012 Architecture, Organization, and Applications<br>RODUCTION 278                                                                                                               | 278 | Memory and the Concept of Tag Field<br>Additional Signal Groups 332 . Soft<br>68020 and 68030 Processors 332                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

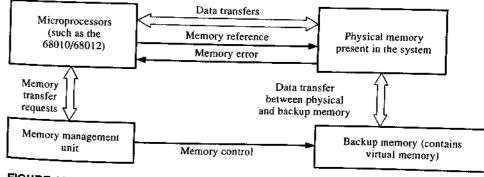

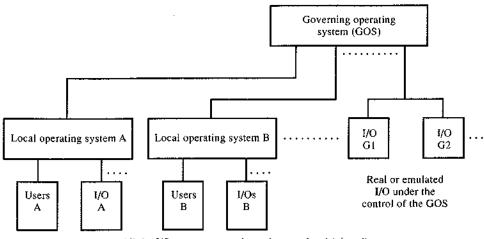

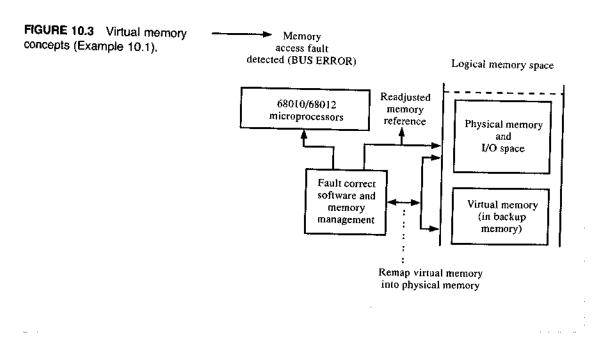

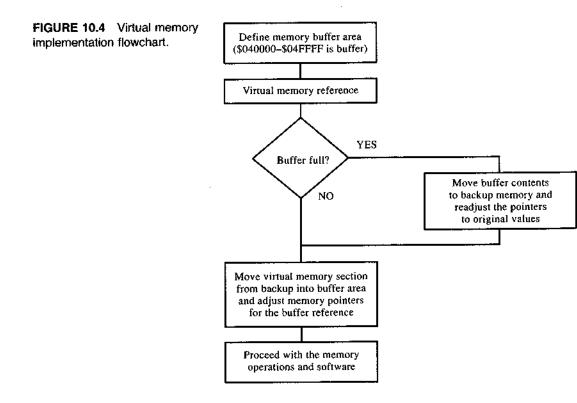

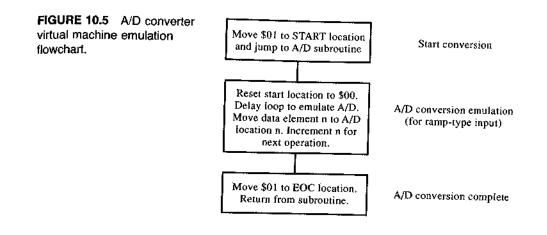

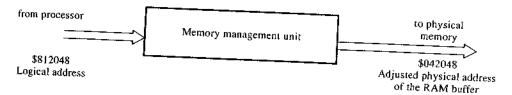

| Virtu                       | TUAL MEMORY AND VIRTUAL MACHINE CONCEPTS279ual Memory Schemes279ual Machine Schemes279                                                                                               |     | 11.6 SUMMARY 334<br>PROBLEMS 335                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

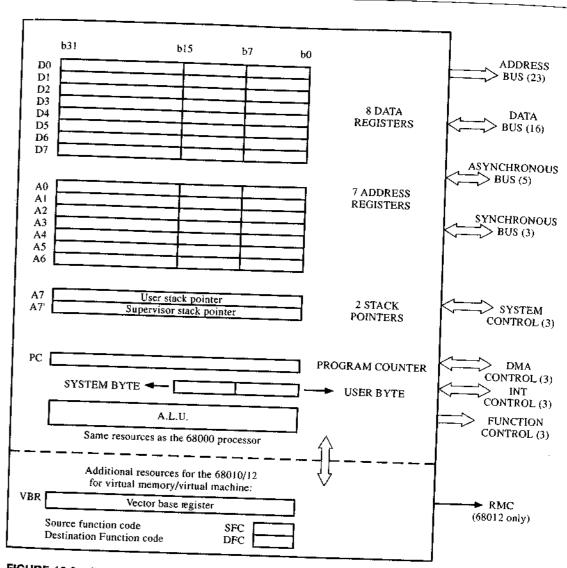

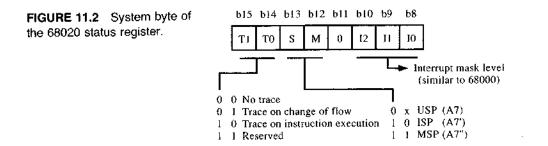

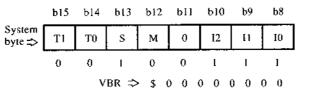

| 10.2 ARC<br>Addi            | CHITECTURE OF THE 68010 AND 68012 MICROPROCESSORS 28<br>itional Register and Busing Resources 284<br>itional Instructions and Modified Instructions 286                              | 34  | ENDNOTES 338                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

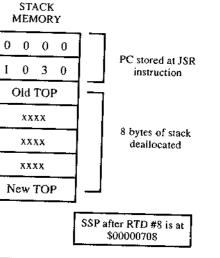

ON SCHEMES 290

thod 290 Correction Methods 291 OCESSING ASSOCIATED 293 Modified Bus Error (BERR) Exception Memory-Related Faults Using Virtual

#### Organization, and Applications

F THE 68020 307 Additional so of the 68020 307 Address,

Interface Schemes 310 MODES AND INSTRUCTIONS ory Indirection Addressing field Type of Instructions Instructions 316 Other

AND ORGANIZATION 320 on and Operation 320 Cache sters 322 F THE 68030 324 ory Organization 324 f the 68030 Processor 326 of the 68030 Processor 327 TS OF THE 68020 331 Memory Indirect Addressing ed Instructions 331 Cache Field 331 The 68020 and 68030 2 . Software Considerations for the

| APPENDIX A:                                                           | 339             |

|-----------------------------------------------------------------------|-----------------|

| Number Systems: Binary and BCD Operations                             | ∧ <sup>a</sup>  |

| APPENDIX B: ", , ", , 68000/10/12 Instruction Set and Condition Codes | q<<br>*«        |

| APPENDIX C: «,                                                        | 40              |

| Analog and Digital Converter Devices for Interface                    | wi              |

| APPENDIX D:                                                           | 42              |

| Instruction Timing for the 68000/10 Processors                        | 41              |

| GLOSSARY                                                              | <b>43</b><br>44 |

| INDEX                                                                 |                 |

q<n \*«\*

431 441

### **INTRODUCTION**

## **The Microprocessor Evolution**

It is no exaggeration to say that the microprocessor device has revolutionized digital electronics and the computer field. Most of the currently available digital, computer, and electronic systems use some form of microprocessor. With processing capability exceeding several million instructions per second (MIPS), the microprocessor is continuously finding new applications.

The earliest form of the microprocessor was a 4-bit device (4004). It was basically used as a 4-bit ALU (arithmetic logic unit) almost a quarter-century ago. The real microprocessor era started in the early 1970s, when Intel Corporation introduced the 8080 microprocessor. This was an 8-bit microprocessor, and contained an ALU and bus interface logic on board. It also had several 8-bit registers for storing operands and addresses. Although the unit required several power supplies and a power-sequencing scheme, it found extensive applications. The success of the 8080 microprocessor led other companies to get involved in the development of different forms of microprocessors.

Immediately after launching the 8080 processor, Intel began to improve its design. which resulted in the 8085. The 8085 processor is code compatible with the earlier 8080, but can operate on a single 5-volt power supply. Almost simultaneously. Motorola Corporation introduced the 8-bit 6800 microprocessor with nonmultiplexed data and address buses. The 6800 processor also incorporates the concept of double accumulators and has an index addressing scheme. The 6800 became an instant success. Several peripheral devices to interface with the 8085 and the 6800 processors were introduced into the market by a number of vendors.

During the mid-1970s, Commodore and Rockwell International introduced the 8bit 6502 microprocessor, which also became an instant success. This machine is similar

to the 6800 processor, but includes additional addressing capabilities such as memory indirect. The design of the Apple computer was based on the 6502 processor. At about the same time, Zilog Corporation introduced the 8-bit Z80 microprocessor. The Z80 is code compatible with the 8085 processor. It has additional resources with which to store data internally, and it also has the index addressing mode of the 6800 and 6502 processors. The Z80 processor found extensive applications in the 8-bit field, even though it entered the 8-bit market late.

Most of the processors we have mentioned were developed with NMOS technology. However ultralow power requirements dictated a processor using CMOS technology. RCA Corporation introduced the first CMOS 8-bit 1802 microprocessor for lowpower applications. Pacemakers and several other battery-powered devices use the 1802 type of processor. Most 8-bit processors have a 64-kilobyte address range.

Emerging applications soon demanded more processing power than 8-bit processors could provide. Intel corporation was again the leader in introducing the first 16-bit 8086 microprocessor in 1978. The internal architecture of the 8086 supports 16-bit operations. The external address bus can access 1 megabyte of memory, which was considered a great advantage. The 8086 has a 16-bit data bus. The 8088 processor is a scaled-down version of the 8086, with an 8-bit data bus. The IBM PC contributed to the great success of the 8086/88 processors.

To follow the 8086 processor, Motorola Corporation introduced the much more powerful and versatile 68000 microprocessor. It has a 16-bit data bus and an effective 24-bit address bus that can access 16 megabytes. The internal architecture of the 68000 is designed to support 8-bit, 16-bit, and 32-bit operations. There are several 32-bit data registers, each of which can be used as an accumulator. The architecture, linear address range, and versatile data-handling capability of the 68000 suited the needs of industry. Systems such as Apple's Macintosh further contributed to the popularity of the 68000 processor. During the same time frame, Zilog corporation introduced its 16-bit Z8000 processor, which is similar to the 68000 in terms of architecture.

Continuous demand by industry resulted in the development of even more powerful processors, such as the 68020 and 68030 in the 68000 family, and the 80386 in the 8086 family. The present trend of development will continue in the 1990s. In order to obtain more dedicated throughput, RISC (reduced instruction set computer chip) devices are becoming popular. But the demand for general-purpose processors will continue to rise.

Also observed in the microprocessor application market is the popularity of singlechip microcomputers and controllers, such as Intel's 8051 and Motorola's 68HC11. These 8-bit devices are suitable for 8-bit I/O interface applications. Sixteen-bit microcontroller devices are also becoming available.

All of the 8-, 16-, and 32-bit processors we have described are available in various packages using different processing techniques

# 16/32–Bit Microprocessors: 68000/68010/68020 Software, Hardware, and Design Applications

Objectives In this chapter we will study:

The 68000 family of microprocessors

Microcomputer configuration of the 68000 family.

Architectural features of the 68000.

Supervisor and user modes of operation

Special features, such as the queue and pipeline

## CHAPTER

# **The 68000 Family of Microprocessors** and Architecture

#### 1.0 INTRODUCTION

The 68000 microprocessor, introduced by Motorola Corporation in the late 1970s, is one of the most powerful and widely used 16/32-bit processors. It is the first member of the 68000 family of processors—a family that includes the 68008, 68010, 68012, 68020, and 68030 processor devices.

Microcomputer configurations based on these processors are similar. In addition, they all have the same basic architecture as that of the 68000. The architecture consists of internal registers and pointers and arithmetic logic and control units.

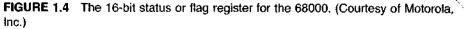

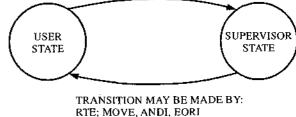

The 68000 operates in two distinct modes: the **supervisor mode** and the **user mode**. These two modes of operation maintain a relative separation between the operating system programs and the user programs.<sup>1</sup>

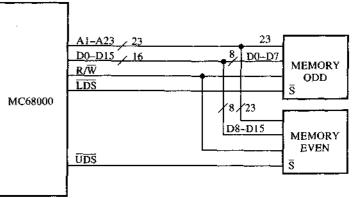

All processors obtain data from the memory block, perform the appropriate operations, and store the resulting data back in the memory. Processors in the 68000 family are structured to handle the **byte** (8-bit), **word** (16-bit), and **long-word** (32-bit) data elements.<sup>2</sup>

An understanding of the architecture, modes of operation, and data-handling schemes is essential to the study of the 68000 microprocessor and associated designs. It will also promote understanding of the other members of the 68000 family.

The material in this chapter will provide the necessary background to understand the software and system features of the 68000 processor. The hardware concepts and designs of the 68000 will be presented in later chapters.

#### 1.1 THE 68000 FAMILY OF MICROPROCESSORS

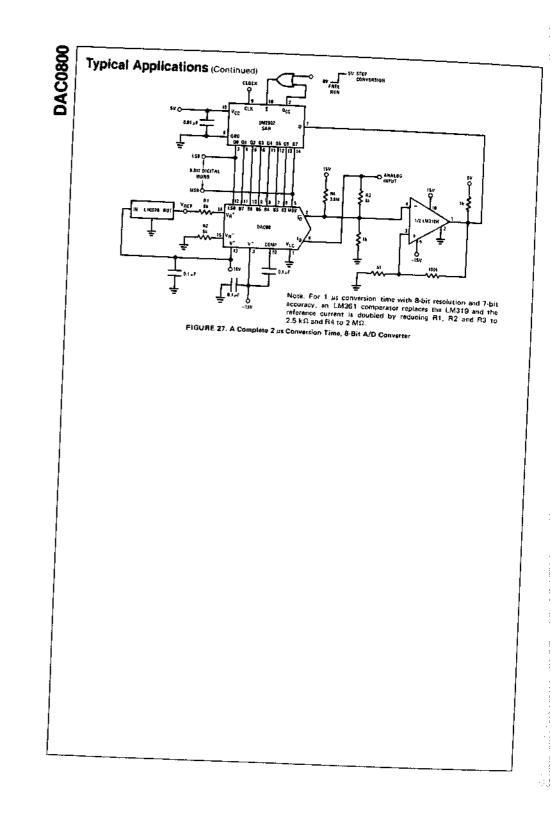

As mentioned previously, all processors in the 68000 family support byte, word, and long-word operations. We will now briefly introduce the important members of the 68000 family. Figure 1.1 illustrates the genealogy of these processors; they are developed using the VLSI (very-large-scale integration) MOS technology.<sup>3</sup>

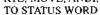

#### The 68000 Microprocessor

The 68000 is the principal device of the 68000 family of microprocessors. The operating frequency of the 68000L4 is 4 MHz; for the 68000L12, the operating frequency is 12 MHz. Several other frequency versions are also available. The 68000 has a 16-bit data bus and an effective 24-bit address bus that supports 16 megabytes of address range. This microprocessor is normally contained in a 64-pin DIP (dual-in-line package), but it is also available in the 68-pin chip-carrier package.

#### The 68008 Microprocessor

The 68008 is the reduced-bus version of the 68000 processor. It has an 8-bit data bus and an effective 20-bit address bus that supports 1 megabyte of address range. The 68008 is contained in a 48-pin DIP. It is very cost effective in applications involving the standard 8-bit I/O (input/output) interface.

FIGURE 1.1 Genealogy of the 68000 family of microprocessors. (Courtesy of Motorola, Inc.)

#### The 68010 Microprocessor

The 68010 is the virtual memory microprocessor. It has all the resources of the 68000 microprocessor. In addition, it has extended internal resources to support the virtual memory management schemes. **Virtual memory** refers to a memory that is not physically present as a part of the system main memory, but is present as a part of the backup memory. This feature allows for error detection and possible error correction in memory access faults.

'I he 68010 is pin compatible with the 68000 microprocessor. The 68000 processor can he replaced with the 68010 in a system without any hardware changes. Additional software can then be written to support the virtual memory schemes.

#### The 68012 Microprocessor

The 68012 is the enhanced virtual memory microprocessor. It is architecturally identical to the 68010. It has an extended address bus that supports 2 gigabytes of address range, as well as additional control lines to support the multiprocessing activity. It is contained in an 84-pin grid-array package.

#### The 68020 Microprocessor

The 68020 is the cache memory microprocessor. In addition to all the resources of the 68010 microprocessor, it has internal resources to support cache memory operation. Cache memory is a fast-access memory that holds prefetched information; thus, it speeds up the system operation. The 68020 is truly a 32-bit microprocessor. It has a 32-bit data bus and a 32-bit address bus that support 4 gigabytes of address range. It also has additional control and interface lines to support the coprocessor interface. It is contained in a 114-pin grid-array package. The 68020 is considered to be one of the best 32-bit microprocessors, and it is one of the most widely used.

#### The 68030 Microprocessor

The 68030 is the enhanced version of the 68020 microprocessor. In addition to all the resources of the 68020, it has internal data cache memory and a memory management unit. These additional resources effectively enhance the throughput of the 68030 processor as compared to the 68020.<sup>4</sup>

#### The 68881 Coprocessor

The architecture of the 68881 coprocessor is different from that of other members of the 68000 family. The 68881 is capable of performing floating-point arithmetic operations to 80-bit precision. It can be interfaced to any member of the 68000 family of processors to increase the arithmetic processing power of the system.

The 68008 is the lowest member and the 68030 is the highest member of the 68000 family of processors. The gradation sequence is  $68008 \rightarrow 68000 \rightarrow 68010 \rightarrow 68012 \rightarrow 68020 \rightarrow 68030$ . These processors are upward code compatible. The software written for a lower level processor will work with a higher level processor. For example, the code written on a 68008-based system will work on a 68000-based system with a similar memory and I/O map. However, the reverse may not be true. Software written for a higher level processor, using the additional resources of that processor, will not work on a lower level processor. For example, the code written on a 68020-based system using the special resources of the 68020 will not work on a 68000-based system, which lacks those resources.<sup>5</sup>

The following example problem will review the concepts we have just discussed with regard to the 68000 family.

#### Example 1.1 The 68000 family of processors.

The 68008 and the 68000 processors support 32-bit internal operations. Their external data buses are 8 and 16 bits wide. Conceptually compute the relative speed of these two processors while transferring

- 1. byte-size data from memory into one of the internal registers of the processor;

- 2. word-size data from memory into one of the internal registers of the processor.

#### Solution

- 1. Byte (8-bit) transfers: The 68008 has an 8-bit data bus and transfers the byte-size data in one unit of time. The 68000 has a 16-bit data bus, out of which only 8 bits are used for byte transfers. Byte transfers, then, still take one unit of time.

- 2. Word (16-bit) transfers: The 68008 transfers a 16-bit word as two bytes. As such, it takes two units of time. By contrast, the 68000 transfers the complete word in one unit of time. Thus, for word transfers, the 68000 processor is twice as fast as the 68008 processor.

The memory and I/O (input/output) interface schemes are similar throughout the 68000 family of processors. This results in a well-structured microcomputer configuration, which we will now introduce.

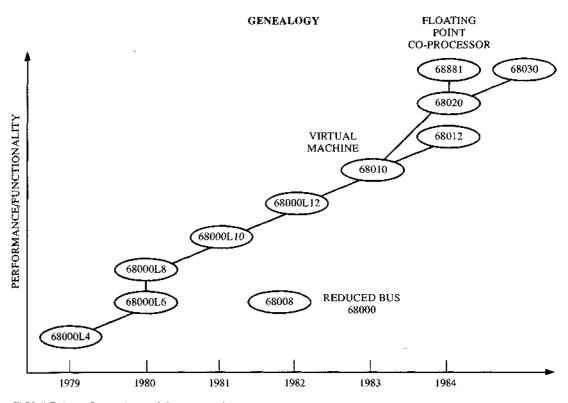

# 1.2 TYPICAL MICROCOMPUTER CONFIGURATION OF THE 68000 FAMILY

Figure 1.2 illustrates the microcomputer configuration typical of the 68000 family. These microprocessors arc of the memory-mapped I/O type, in which the microprocessor communicates with an I/O device as if it were one of the memory locations. However, there are some special instructions in the 68000 family to efficiently deal with I/O data.

#### General Interface Scheme

Each member of the family has appropriate control and interface buses to support the synchronous and the asynchronous devices and systems, as shown in Figure 1.2. A bus is a group of signal lines. In the synchronous type of interface, data transfers take place upon certain clocking or timing events. The peripheral devices belonging to such earlier 8 bit processors as the 8085, 6800, and Z80 operate in this manner. In the asynchronous type of interface, data transfers take place via handshaking. In this protocol, the responding device provides an acknowledgment signal to the processor during data transfer... Most of the peripherals belonging to the 68000 family and the static memory follow this protocol."

There are also special interfaces. The interrupt mechanism is the traditional means by which to gain the attention of the processor by a slow I/O device. The DMA (direct memory access) is the traditional means by which to effect high-speed data transfers between the memory and I/O without the intervention of the microprocessor. I-icn member of the 68000 family supports both of these features explicitly. The system control interface consists of the reset, halt, and bus error detection functions. The other interlaces of the processor consist of the clock distribution network, system power distribution network, and the address decoding network. Details of all these functions will be discussed in later chapters.

FIGURE 1.2 Typical microcomputer configuration of the 68000 family of microprocessors. (Courtesy of Motorola, Inc.)

#### Typical 68000-Based Systems

The Macintosh from Apple Computers, Inc., the Amiga from Commodore, Inc., the ST from Atari, and the 9716 from Hewlett-Packard are some of the most popular microcomputer systems based on the 68000 microprocessor. The MEX68KECB microcomputer module from Motorola is an excellent 68000-based educational computer for learning the software and hardware features of the 68000 microprocessor and associated system designs.

An existing microcomputer system with a lower level processor can be upgraded to a higher performance processor with appropriate modifications. This is feasible because of the upward code compatibility.

The following example problem will review our discussion of the 68000-based system configuration.

#### *Example 1.2* 68000-based systems.

The 68000-based microcomputer is used in a control-system application. The processor is required to interface with the 8-bit I/O peripherals belonging to the earlier 6800 and Z80 type of processors. These devices respond to appropriate clocking events.

- 1. What is the preferred type of interface in the 68000? Why?

- 2. Suppose the 68000 system needs to be upgraded to the 68010. What additional hardware and software resources are required to accomplish this task?

#### Solution

- since these devices are of the synchronous type.

Existing software will function on the upgraded system. However, to make full use of the capabilities of the 68010, virtual memory software should be utilized.

The processing activity of a microprocessor depends on its architecture and how its internal resources are organized. The 68000 processor is rich in internal resources and has a 32-bit internal register architecture. We will now introduce these important concepts.

#### **1.3 GENERAL ARCHITECTURE OF THE** 68000 MICROPROCESSOR

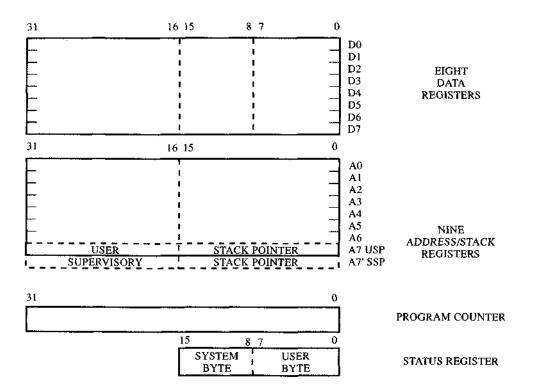

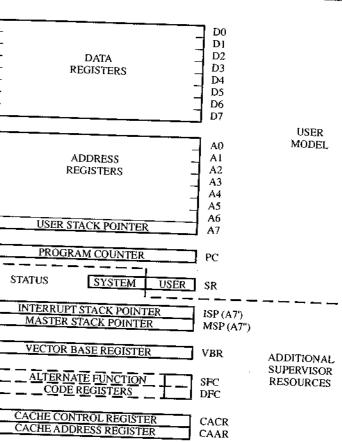

The architecture of the 68000 microprocessor serves as the prototype on which all the other processors in the family are based. Figure 1.3 illustrates this internal architecture. It includes the following features:

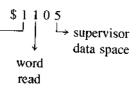

> eight 32-bit data seven 32-bit ad two 32-bit stack user stack supervisor one 32-bit progr

one 16-bit status

In addition, the 68000 contains a 32-bit arithmetic logic unit (ALU), an instruction decoding unit, a control unit, a bus interface unit, and an execution unit. For the sake of simplicity, these resources are not indicated in the figure. For the 32-bit registers and the data structures, the byte corresponds to the lower 8 bits, the word corresponds to the lower l6 bits, and the long word corresponds to all of the 32 bits. We will now provide a functional description of the basic features.

#### Data Registers D0-D7 (Dn)

These eight data registers are for general-purpose data storage and processing. They handle bytes (8 bits), words (16 bits), and long words (32 bits) of data. Each of these registers can function as an accumulator. An **accumulator** is a special register that provides data operands to the ALU and stores the result from the ALU. In addition, any of

1. Interfacing the 6800 and Z80 peripherals: Synchronous interface is preferred,

2. Upgrading to the 68010: No additional hardware is required. However, to make full use of the capabilities of the 68010, memory management units may be added.

| a registers, D0-D7         | (Dn)  |

|----------------------------|-------|

| ddress registers, A0-A6    | (An)  |

| k pointers:<br>pointer, A7 | (USP) |

| y stack pointer, A7'       | (SSP) |

| ram counter                | (PC)  |

| s register                 | (SR)  |

FIGURE 1.3 The internal architecture of the 68000. (Courtesy of Motorola, Inc.)

the data registers can be used for memory indexing, a process in which a number in the data register is added to the base address to obtain the effective address of the data operand. Operations on the data register operands affect the flag bits in the status register.

### Address Registers A0-A6 (An)

These seven address registers function as address **pointers.** They store and operate on word- and long-word address operands. By means of these address operands, memory can be accessed. The address registers also can be used for general-purpose storage of operands of word and long-word size, as well as for memory indexing. The address registers do not support the byte operands. Operations on the address register operands will not affect the flag bits in the status register (except in compare-type operations).

### Stack Pointers A7 (USP) and A7' (SSP)

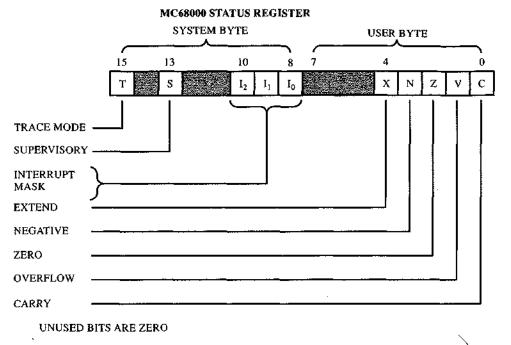

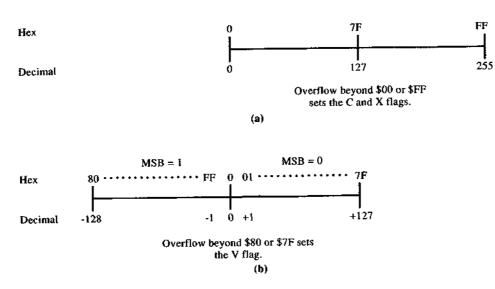

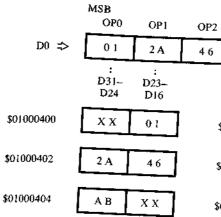

As previously mentioned, the 68000 microprocessor operates in two distinct modes called the user mode and the supervisor mode. The former deals with user programs; the latter, with system-level programs. In order to maintain a distinction between these modes, the 68000 has two 32-bit stack pointers: the **user stack pointer (USP** or A7)