## Errata for the

## Amiga Hardware Manual

The attached documents contain various updates to the Amiga Hardware Manual. The documents are:

Changes and Additions

Read this first; it contains miscellaneous corrections and is a guide to all of the updates.

Examples

Contains example assembly code sequences for the Copper, playfields, and sprites.

Addendum to Chapter 5: Audio Hardware Describes the audio state machine.

Addendum to Chapter 6: Blitter Hardware Describes blitter DMA and how the operation of the blitter affects the performance of the rest of the system.

Appendix F This replaces the present Appendix F.

Appendix G This replaces the present Appendix G.

## Changes and Additions to the Amiga Hardware Manual

Changes and additions have been made to the following chapters and appendixes of the Amiga Hardware Manual.

#### Chapter 2: Coprocessor Hardware

Add the examples in the attached document called "Examples for the Amiga Hardware Manual".

## Chapter 3: Playfield Hardware

Add the examples in the attached document called "Examples for the Amiga Hardware Manual".

## Chapter 4: Sprite Hardware

Add the examples in the attached document called "Examples for the Amiga Hardware Manual".

On page 4-14, under section 4.3, "Displaying a Sprite", add the following:

#### CAUTION

Should sprite DMA be turned off while a sprite is being displayed (that is, after VSTART but before VSTOP), the system will continue to display the line of sprite data that was most recently fetched. This causes a vertical bar to appear on the screen. It is recommended that sprite DMA only be turned off during vertical blanking or during some portion of the screen where you are *sure* that no sprite is being displayed.

## Chapter 5: Audio Hardware

Add the attached document called "Addendum to Chapter 5: Audio Hardware".

#### Chapter 6: Blitter Hardware

Add the attached document called "Addendum to Chapter 6: Blitter Hardware".

On page 6-14, under section 6.11, "Line Drawing", add the following line to the table:

| Register<br>Name | Bit<br>Number | Bit<br><u>Name</u> | State | Purpose                     |

|------------------|---------------|--------------------|-------|-----------------------------|

| BLTCON1          | 5             |                    | 0     | Reserved for flabloden mode |

On page 6-8, add the following to section 6.6, "Ascending and Descending Addressing":

If the source and destination data areas overlap in a blitter operation, there is a possibility of writing to a particular location as the destination before it was read as the source.

To prevent this kind of data destruction, you must take care to correctly choose ascending or descending mode, and possibly you should offset the source or destination.

Some types of overlapped blitter moves will always result in damaged data; therefore, the desired move must be done in two steps:

- 1. Move to a safe place.

- 2. Move to desired destination.

Using the blitter Memory Bus Activity Table<sup>1</sup>, you can observe the order of operations and determine the required offset or mode. Pay careful attention to the notes. It helps to draw pictures.

<sup>&</sup>lt;sup>1</sup> This table is located in the separate "Addendum to the Blitter Hardware Chapter" attached to this document.

### Chapter 8: Interface Hardware

On page 8-4, under "Counter Limitations", the last line should read:

\*\* 45-200 = -155. Because the absolute value exceeds 127, the true count must be

## Appendix A

On page 4, in the table called "LINE MODE (line draw)", change the following bits for BLTCON1:

| BIT#                 | BLTCON0                              | BLTCON1                                      |                            |

|----------------------|--------------------------------------|----------------------------------------------|----------------------------|

| 15<br>14<br>13<br>13 | START3<br>START2<br>START1<br>START0 | TEXTURE3<br>TEXTURE2<br>TEXTURE1<br>TEXTURE0 |                            |

| 05                   | LF5                                  | 0                                            | (Reserved for<br>new mode) |

On page 5, in the table called "LINE MODE (line draw)", change the line beginning "OVF ..." to: 0 Reserved for new mode

At the end of the same table, add:

The "B" source is used for texturing the drawn lines.

#### Appendix B

On page 2, after "BLTCDAT", "BLTBDAT", and "BLTADAT", change "&" to "%".

## Appendix F

Remove Appendix F and insert the attached new Appendix F. Appendix F contains a new front section, called "Brief address map for 8520's".

## Appendix G

Remove Appendix G and insert the attached new Appendix G. Appendix G has some minor changes.

Since this appendix is subject to change, anyone who is actually designing a device to interface to the Amiga should contact Amiga Third-Party Support.

## Appendix I

This is a new appendix. It describes the interface to the 68000 bus connector.

## Appendix F

Remove Appendix F and insert the attached new Appendix F. Appendix F contains a new front section, called "Brief address map for 8520's".

## Appendix G

Remove Appendix G and insert the attached new Appendix G. Appendix G has some minor changes.

Since this appendix is subject to change, anyone who is actually designing a device to interface to the Amiga should contact Amiga Third-Party Support.

## Appendix I

This is a new appendix. It describes the interface to the 68000 bus connector.

## Examples for the

## Amiga Hardware Manual

#### Chapter 2: Coprocessor Hardware

Add the following example to page 2-4, under section 2.3, "The MOVE Instruction".

The following MOVE instructions point bit-plane pointer 1 at \$21000 and bitplane pointer 2 at \$25000.

| DC.W | \$00E0,\$0002 | ;MOVE \$0002 TO ADDRESS \$0E0 (BPL1PTH) |

|------|---------------|-----------------------------------------|

| DC.W | \$00E2,\$1000 | ;MOVE \$1000 TO ADDRESS \$0E2 (BPL1PTL) |

| DC.W | \$00E4,\$0002 | ;MOVE \$0002 TO ADDRESS \$0E4 (BPL2PTH) |

| DC.W | \$00E6,\$5000 | ;MOVE \$5000 TO ADDRESS \$0E6 (BPL2PTL) |

Add the following examples to page 2-5, under section 2.4, "The Wait Instruction".

This first WAIT instruction waits for scan line 150 (96 hex) with the horizontal position masked off.

DC.W \$9601,\$FF00 ;WAIT FOR LINE 150, IGNORE HORIZONTAL COUNTERS

This second WAIT instruction waits for scan line 255 and horizontal position 254. This will never occur, so the copper stops until the next vertical blanking interval begins.

DC.W FFFF,FFFE; WAIT FOR LINE 255, H = 254 (ENDS COPPER LIST).

Add the following example to page 2-10, under section 2.6, "Putting Together a Copper Instruction List".

This is an example of a complete Copper list. It is a Copper list for two bit-planes, one at \$21000, one at \$25000. At the top of the screen, the color registers are set as follows:

COLOR00 = WHITE COLOR01 = RED COLOR02 = GREENCOLOR03 = BLUE

At line 150, the color registers are reloaded as follows:

$\bullet$ COLOR00 = BLACK COLOR01 = YELLOWCOLOR02 = CYANCOLOR03 = MAGENTA**COPPERLIST:** DC.W \$00E0,\$0002 ;MOVE \$0002 INTO ADDRESS \$0E0 (BPL1PTH) DC.W \$00E2,\$1000 :MOVE \$1000 INTO ADDRESS \$0E2 (BPL1PTL) DC.W \$00E4,\$0002 ;MOVE \$0002 INTO ADDRESS \$0E4 (BPL2PTH) DC.W \$00E6,\$5000 ;MOVE \$5000 INTO ADDRESS \$0E6 (BPL2PTL) ; Load color registers DC.W \$0180,\$0FFF ;MOVE WHITE INTO ADDRESS \$180 (COLOR00) DC.W \$0182,\$0F00 ;MOVE RED INTO ADDRESS \$182 (COLOR01) DC.W \$0184,\$00F0 ;MOVE GREEN INTO ADDRESS \$184 (COLOR02) DC.W ;MOVE BLUE INTO ADDRESS \$186 (COLOR03) \$0186,\$000F : Wait for line 150 DC.W \$9601,\$FF00 ;WAIT FOR LINE 150, IGNORE HORIZ. POSITION ; Reload color registers DC.W \$0180,\$0000 ;MOVE BLACK INTO ADDRESS \$0180 (COLOR00) DC.W \$0182,\$0FF0 ;MOVE YELLOW INTO ADDRESS \$0182 (COLOR01) DC.W \$0184,\$00FF ;MOVE CYAN INTO ADDRESS \$0184 (COLOR02) DC.W \$0186,\$0F0F ;MOVE MAGENTA INTO ADDRESS \$0186 (COLOR03) ; End copper list by waiting for the impossible DC.W **\$FFFF**, **\$FFFE** ; WAIT FOR LINE 255, H = 254 (NEVER HAPPENS)

Add the following to page 2-13, under section 2.8.1, "The SKIP Instruction".

The following SKIP instruction will skip the instruction following it if VP >= 100 (\$64).

DC.W \$6401,\$FF01; IF VP >= 100,SKIP NEXT INSTR (IGNORE HP). DC.W ....this is the instruction that will be skipped....

Replace the example on page 2-14, under section 2.8.2, "Copper Loops and Branches and Comparison Enable", with the following:

: Copper list to interrupt 68000 once every 16 scan lines, ; in the range VP = 80 through VP = 160. ; DC.W \$5001,\$FFFE ;WAIT FOR VP =\$50, HP = 0\$0F01,\$0F00 ;WAIT FOR VP = xxxx1111DC.W ; The following instruction writes to address \$09C, the ; interrupt request register. Writing \$8010 sets the copper ; interrupt bit in the register, which will interrupt the 68000. DC.W \$009C,\$8010 ;MOVE \$8010 TO \$09C (INTERRUPT 68000) DC.W \$A001,\$FF01 ;SKIP NEXT INSTRUCTION IF VP >= 160; The next MOVE instruction doesn't actually do a move. It forces ; the copper to jump to the address in COP2LC. This must have been ; previously set by either the copper or the 68000. If VP >= 160, ; then this instruction will be skipped. ; DC.W \$008A.\$0000 ;MOVE 0 TO COPJMP2 (COP2LC PREVIOUSLY SET) DC.W ... other copper instructions

#### Chapter 3: Playfield Hardware

Add this example to page 3-10, under "Selecting Number of Bit-Planes".

This example shows how to write to the BPLCON0 register to tell the system to use 2 bitplanes.

| ;<br>; Writing \$2200 to BPLCON0 sets the f | ollowing conditions: |  |

|---------------------------------------------|----------------------|--|

| ; Low Resolution                            |                      |  |

| ; Use two bitplanes                         |                      |  |

| ; Hold-and-modify $mode = OFF$              |                      |  |

| ; Single playfield mode                     |                      |  |

| ; Composite video color enabled             |                      |  |

| ; Genlock audio disabled                    |                      |  |

| ; Light pen disabled                        |                      |  |

| ; Interlace disabled                        |                      |  |

| ; External resync disabled                  |                      |  |

| ;                                           |                      |  |

| BPLCON0 EQU \$DFF100                        | ;BPLCON0 ADDRESS     |  |

| MOVE.W #\$2200,BPLCON0                      | ;WRITE TO IT         |  |

Add the following example to page 3-10, under section 3.2.3, "Selecting Horizontal and Vertical Resolution".

This example shows how to set the HIRES and LACE bits.

Writing \$A204 to BPLCON0 sets the following conditions:

High resolution

Use two bitplanes

Hold-and-modify mode = OFF

Single playfield mode

Composite video color enabled

Genlock audio disabled

Light pen disabled

Interlace enabled

External resync disabled

BPLCON0 EQU \$DFF100 ;BPLCON0 ADDRESS

MOVE.W #\$A204,BPLCON0 ;WRITE TO IT

Add the following example to page 3-12, under section 3.2.4, "Allocating Memory for Bit-Planes"

This example shows how to set pointers for memory allocation for bit-planes.

|                                                                                                   | t \$21000 and the other at \$25000, the processor<br>PL2PT to \$25000. Normally, this is the copper's                                              |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| ;<br>BPL1PTH EQU \$DFF0E0<br>BPL1PTL EQU \$DFF0E2<br>BPL2PTH EQU \$DFF0E4<br>BPL2PTL EQU \$DFF0E6 | ;HIGH THREE BITS OF BITPLANE 1 POINTER REGISTE<br>;LOW FIFTEEN BITS<br>;HIGH THREE BITS OF BITPLANE 2 POINTER REGISTE<br>;LOW FIFTEEN BITS         |

| ; a single longword move. The                                                                     | o write to a bitplane pointer, but we can use<br>68000 writes the high order word to the lower-<br>) and the low order word to the higher-numbered |

| ;<br>MOVE.L #\$21000,BPL1<br>MOVE.L #\$25000,BPL2                                                 | ,                                                                                                                                                  |

Add the following examples to page 3-15, under "A One- or Two-Color Playfield"

This example shows how to define a 1-color bit-plane.

; ; This code fills a low resolution bit-plane with the background color (COLOR00) ; by writing all 0's into its memory area. The bitplane starts at \$21000 and ; is 8000 bytes long. ; LEA \$21000,A0 ;POINT AT BITPLANE MOVE.W #2000,D0 ;WRITE 2000 LONGWORDS = 8000 BYTES LOOP: MOVE.L #0,(A0)+ ;WRITE OUT A ZERO SUBQ.W #1,D0 ;DECREMENT COUNTER

;LOOP UNTIL BITPLANE IS FILLED WITH 0'S

This example shows how to define a 2-color bit-plane.

BNE LOOP

; This code is identical to the last example, except the bitplane is filled ; with \$FF00FF00 instead of all 0's. This will produce two colors.

LEA \$21000,A0 ;POINT AT BITPLANE MOVE.W #2000,D0 ;WRITE 2000 LONGWORDS = 8000 BYTES LOOP: MOVE.L #\$FF00FF00,(A0)+ ;WRITE OUT \$FF00FF00 SUBQ.W #1,D0 ;DECREMENT COUNTER BNE LOOP ;LOOP UNTIL BITPLANE IS FULL

Add this example to page 3-18, under "Setting the Display Window Starting Position".

Setting DIWSTRT for the basic playfield:

; This code sets DIWSTRT for a basic playfield. We write \$2C for the vertical ; position and \$81 for the horizontal position.

DIWSTRT EQU \$DFF08E ;DISPLAY WINDOW START REGISTER ADDRESS

MOVE.W #\$2C81,DIWSTRT ;WRITE IT OUT

Add this example to page 3-19, under "Setting the Display Window Stopping Position".

Setting DIWSTOP for the basic playfield:

; This code sets DIWSTOP for a basic playfield. We write \$F4 for ; the vertical position and \$C1 for the horizontal position.

DIWSTOP EQU \$DFF090 ;DISPLAY WINDOW STOP REGISTER ADDRESS ; MOVE.W #\$F4C1,DIWSTOP ;WRITE IT OUT

Add the following examples to page 3-19, under Section 3.2.7, "Telling the System How to Fetch and Display Data".

Setting data fetch for the basic playfield:

; This code sets the data fetch start and stop values for a basic ; playfield. We write \$0038 to DDFSTRT and \$00D0 into DDFSTOP. ; DDFSTRT EQU \$DFF092 DDFSTOP EQU \$DFF094 ; MOVE.W #\$0038,DDFSTRT ;WRITE TO DDFSTRT MOVE.W #\$00D0,DDFSTOP ;WRITE TO DDFSTOP

Setting modulo for the basic playfield:

; This code sets the modulo to 0 for a low resolution playfield with one ; bitplane. For this example, the bitplane is one of the odd-numbered ; ones. We would write to BPL2MOD for even-numbered bitplanes. ; BPL1MOD EQU \$DFF108 ;MODULO FOR ODD BITPLANES ; MOVE.W #0,BPL1MOD ;SET MODULO TO 0

Add the following examples to page 3-26, under a new section, 3.2.11, "Complete Example Playfields".

; This first example sets up a 320 x 200 pixel playfield with ; one bitplane. ; The bitplane lives at \$21000. ; We also set up a copper list at \$20000. CUSTOM EQU \$DFF000 BPLCON0 EQU \$100 BPLCON1 EQU \$102 BPLCON2 EQU \$104 BPL1MOD EQU \$108 DDFSTRT EQU \$092 DDFSTOP EQU \$094 DIWSTRT EQU \$08E DIWSTOP EQU \$090 VPOSR EQU \$004 COLOR00 EQU \$180

COLOR01 EQU \$182

```

COLOR02 EQU $184

COLOR03 EQU $186

DMACON EQU $096

COPPER LOCATION REGISTER 1 (HIGH 3 BITS)

COP1LCH EQU $080

;A0 POINTS AT CUSTOM CHIPS

LEA CUSTOM, A0

MOVE.W #$1200,BPLCON0(A0)

ONE BITPLANE, ENABLE COMPOSITE COLOR

MOVE.W #0,BPLCON1(A0)

SET HORIZONTAL SCROLL VALUE TO 0

SET MODULO TO 0 FOR ALL ODD BITPLANES

MOVE.W #0,BPL1MOD(A0)

MOVE.W #$0038,DDFSTRT(A0)

SET DATA FETCH START TO $38

MOVE.W #$00D0,DDFSTOP(A0)

SET DATA FETCH STOP STOP TO $D0

SET DIWSTRT TO $2C81

MOVE.W #$2C81,DIWSTRT(A0)

MOVE.W #$F4C1,DIWSTOP(A0)

SET DISPLAY WINDOW STOP TO $F4C1

MOVE.W #$0F00,COLOR00(A0)

SET BACKGROUND COLOR TO RED

MOVE.W #$0FF0,COLOR01(A0)

SET COLOR REGISTER 1 TO YELLOW

; FILL BITPLANE WITH $FF00FF00 TO PRODUCE STRIPES

POINT AT BEGINNING OF BITPLANE

MOVE.L #$21000,A1

MOVE.L #$FF00FF00,D0

;WE WILL WRITE $FF00FF00 LONG WORDS

MOVE.W #2000,D1

2000 \text{ LONG WORDS} = 8000 \text{ BYTES}

MOVE.L D0(A1)+

WRITE A LONG WORD

LOOP:

DECREMENT COUNTER

SUBQ.W #1,D1

:LOOP UNTIL BITPLANE IS FILLED

BNE LOOP

; Set up copper list at $20000

POINT AT COPPER LIST DESTINATION

MOVE.L #$20000,A1

LEA COPPERL, A2

POINT A2 AT COPPER LIST DATA

;MOVE A WORD

CLOOP: MOVE.L (A2),(A1)+

#$FFFFFFE,(A2)+ ;CHECK FOR LAST LONGWORD OF COPPER LIST

CMPI.L

BNE CLOOP

LOOP UNTIL ENTIRE COPPER LIST IS MOVED

; Point copper at copper list

MOVE.L #$20000,COP1LCH(A0)

WRITE TO COPPER LOCATION REGISTER

FORCE COPPER TO $20000

MOVE.W COPJMP1(A0),D0

; Start DMA

MOVE.W #$8380,DMACON(A0)

;ENABLE BITPLANE AND COPPER DMA

;GO DO NEXT TASK

BRA ....

```

; This is the data for the copper list.

## COPPERL:

| DC.W | \$00E0,\$0002        | ;MOVE \$0002 TO ADDRESS \$0E0 (BPL1PTH) |

|------|----------------------|-----------------------------------------|

| DC.W | \$00E2,\$1000        | ;MOVE \$1000 TO ADDRESS \$0E2 (BPL1PTL) |

| DC.W | <b>\$FFFF,\$FFFE</b> | END OF COPPER LIST                      |

| 200  |                      |                                         |

;

```

This second example of a basic playfield sets up a hi resolution, interlaced

display with one bitplane.

The equates are the same as the previous example so they aren't repeated here.

;ADDRESS OF CUSTOM CHIPS

LEA CUSTOM, A0

MOVE.W #$9204,BPLCON0(A0)

HIRES, 1 BITPLANE, INTERLACE

MOVE.W #0,BPLCON1(A0)

;HORIZONTAL SCROLL VALUE = 0

MODULO = 80 FOR ODD BITPLANES

MOVE.W #80,BPL1MOD(A0)

DITTO FOR EVEN BITPLANES

MOVE.W #80,BPL2MOD(A0)

MOVE.W #$003C,DDFSTRT(A0)

SET DATA FETCH START FOR HI RES

SET DATA FETCH STOP

MOVE.W #$00D4,DDFSTOP(A0)

SET DISPLAY WINDOW START

MOVE.W #$2C81,DIWSTRT(A0)

MOVE.W #$F4C1,DIWSTOP(A0)

SET DISPLAY WINDOW STOP

; Set up color registers

MOVE.W #$000F,COLOR00(A0)

; BACKGROUND COLOR = BLUE

:FOREGROUND COLOR = WHITE

MOVE.W #$0FFF,COLOR01(A0)

; Set up bitplane at $20000.

;

POINT A1 AT BITPLANE

LEA $20000,A1

:A2 POINTS AT CHARACTER DATA

LEA CHARLIST,A2

;WRITE 400 LINES OF DATA

MOVE.W #400,D1

WRITE 20 LONG WORDS PER LINE

MOVE.W #20,D0

L1:

WRITE A LONG WORD

MOVE.L (A2),(A1)+

SUBQ.W #1,D0

;DECREMENT COUNTER

LOOP UNTIL LINE IS FULL

BNE L1

;

MOVE.W #20,D0

RESET LONG WORD COUNTER

POINT AT NEXT WORD IN CHAR LIST

ADDQ.L #4,A2

;END OF CHAR LIST?

\#$FFFFFFFF,(A2)

CMPI.L

```

```

BNE L2

YES, RESET A2 TO BEGINNING OF LIST

LEA CHARLIST, A2

L2:

DECREMENT LINE COUNTER

SUBQ.W #1,D1

;LOOP UNTIL ALL LINES ARE FULL

BNE L1

; Start DMA

MOVE.W #$8300,DMACON(A0)

ENABLE BITPLANE DMA ONLY, NO COPPER.

: Since this example has no copper list, we sit in a loop waiting for vertical

; blank. When it comes, we check the LOF (long frame) bit in VPOSR. If it

; is a 0, then this is a short frame so we point the bitplane pointers to

; $200050; if LOF = 1, then this is a long frame so we point to $20000. This

; keeps the long and short frames in the right relationship to each other.

VLOOP:

READ INTERRUPT REQUESTS

MOVE.W INTREQR(A0),D0

#$0020,D0

MASK OFF ALL BUT VERTICAL BLANK

AND.W

LOOP UNTIL VERTICAL BLANK COMES

BEQ VLOOP

RESET VERTICAL INTERRUPT

MOVE.W #$0020,INTREQ(A0)

READ LOF BIT INTO DO BIT 15

MOVE.W VPOSR(A0),D0

; IF LOF = 0, JUMP

BPL VL1

MOVE.L #$20000,BPL1PTH(A0)

;LOF = 1, POINT TO 20000

BACK TO TOP

BRA VLOOP

VL1:

MOVE.L #$20050,BPL1PTH(A0)

LOF = 0, POINT TO $20050

;BACK TO TOP

BRA VLOOP

Character list

DC.L $18FC3DF0,$3C6666D8,$3C66C0CC,$667CC0CC

DC.L $7E66C0CC,$C36666D8,$C3FC3DF0,$0000000

DC.L $FFFFFFF

```

Add the following example to page 3-50, under "Specifying the Amount of Delay".

Setting the delay for horizontal scrolling:

This code sets the horizontal scroll delay to 7 for both playfields.

BPLCON1 EQU \$DFF102 ;HORIZONTAL SCROLL REGISTER ;

MOVE.W #\$77,BPLCON1

Add the following example to page 3-52, under section 3.6.2, "Hold and Modify Mode".

Hold and modify example:

```

: This code generates a six bit-plane display with hold-and-modify mode

turned on. We load all 32 color registers with black to prove that

; the colors are being generated by hold-and-modify.

; The equates are the usual, so we won't repeat them here.

; First we set up the control registers.

POINT A0 AT CUSTOM CHIPS

LEA CUSTOM, A0

MOVE.W #$6A00,BPLCON0(A0)

SIX BITPLANES, HOLD AND MODIFY MODE

MOVE.W \#0,BPLCON1(A0)

;HORIZONTAL SCROLL = 0

;MODULO FOR ODD BITPLANES = 0

MOVE.W #0,BPL1MOD(A0)

MOVE.W #0,BPL2MOD(A0)

DITTO FOR EVEN BITPLANES

MOVE.W #$0038,DDFSTRT(A0)

SET DATA FETCH START

MOVE.W #$00D0,DDFSTOP(A0)

SET DATA FETCH STOP

SET DISPLAY WINDOW START

MOVE.W #$2C81,DIWSTRT(A0)

SET DISPLAY WINDOW STOP

MOVE.W #$F4C1,DIWSTOP(A0)

; Set all color registers = black to prove hold and modify mode is working.

;INITIALIZE COUNTER

MOVE.W #32,D0

LEA CUSTOM+COLOR00,A1 ;POINT A1 AT FIRST COLOR REGISTER

CREGLOOP:

WRITE BLACK TO A COLOR REGISTER

MOVE.W \#$0000,(A1)+

:DECREMENT COUNTER

SUBQ.W #1,D0

BNE CREGLOOP

LOOP UNTIL ALL COLOR REGISTERS SET.

; Fill six bitplanes with an easily recognizable pattern.

MOVE.W #2000,D0

;2000 LONGWORDS PER BITPLANE

MOVE.L #$21000,A1

;POINT A1 AT BIT PLANE 1

```

```

POINT A2 AT BIT PLANE 2

MOVE.L #$23000,A2

POINT A3 AT BIT PLANE 3

MOVE.L #$25000,A3

MOVE.L #$27000,A4

POINT A4 AT BIT PLANE 4

POINT A5 AT BIT PLANE 5

MOVE.L #$29000,A5

POINT A6 AT BIT PLANE 6

MOVE.L #$2B000,A6

FPLLOOP:

;FILL BIT PLANE 1 WITH $55555555

MOVE.L #$55555555,(A1)+

FILL BIT PLANE 2 WITH $33333333

MOVE.L #$33333333(A2)+

MOVE.L \#$0F0F0F0F,(A3)+

FILL BIT PLANE 3 WITH $0F0F0F0F

MOVE.L \#$00FF00FF,(A4)+

FILL BIT PLANE 4 WITH $00FF00FF

MOVE.L #$FFFFFFF,(A5)+ ;FILL BIT PLANE 5 WITH $FFFFFFF

MOVE.L #$0000000,(A6)+

;FILL BIT PLANE 6 WITH $00000000

:DECREMENT COUNTER

SUBQ.W #1,D0

;LOOP UNTIL ALL BIT PLANES ARE FULL.

BNE FPLLOOP

; Set up a copper list at $20000.

POINT A1 AT COPPER LIST DESTINATION

MOVE.L #$20000,A1

POINT A2 AT COPPER LIST IMAGE

LEA COPPERL, A2

CLOOP: MOVE.L (A2),(A1)+

MOVE A LONG WORD

#$FFFFFFE,(A2)+ ;CHECK FOR END OF COPPER LIST

CMPI.L

LOOP UNTIL ENTIRE COPPER LIST MOVED.

BNE CLOOP

; Point copper at copper list

MOVE.L #$20000,COP1LCH(A0)

LOAD COPPER JUMP REGISTER

MOVE.W COPJMP1(A0),D0

FORCE LOAD INTO COPPER P.C.

; Start DMA

MOVE.W #$8380,DMACON(A0)

ENABLE BITPLANE AND COPPER DMA

BRA .....next stuff to do.....

; Copper list for six bit planes. Bit plane 1 is at $21000, 2 is at $23000,

; 3 is at $25000, 4 is at $27000, 5 is at $29000, 6 is at $28000.

COPPERL:

DC.W

;BIT PLANE 1 POINTER = $21000

$00E0,$0002

DC.W

$00E2,$1000

BIT PLANE 2 POINTER = $23000

DC.W

$00E4,$0002

DC.W

$00E6,$3000

;BIT PLANE 3 POINTER = $25000

DC.W

$00E8,$0002

DC.W

$00EA,$5000

BIT PLANE 4 POINTER = $27000

DC.W

$00EC,$0002

```

| DC.W | \$00EE,\$7000        |                                      |

|------|----------------------|--------------------------------------|

| DC.W | \$00F0,\$0002        | BIT PLANE 5 POINTER = \$29000        |

| DC.W | <b>\$00F2,\$9000</b> |                                      |

| DC.W | <b>\$00F4,\$0002</b> | ;BIT PLANE 6 POINTER = \$2B000       |

| DC.W | \$00F6,\$B000        |                                      |

| DC.W | \$FFFF,\$FFFE        | ;WAIT FOR THE IMPOSSIBLE, I.E., QUIT |

## Chapter 4: Sprite Hardware"

Add the following example of a sprite data structure to page 4-9, under "Building the Data Structure".

; The following data is the data structure for the spaceship sprite. It

; will be located at V = 65 and H = 128 on the screen.

SPRITE:

| RITE: |                        |                                |

|-------|------------------------|--------------------------------|

| DC.W  | \$6D60,\$7200          | ;VSTART, HSTART, VSTOP         |

| DC.W  | \$0990,\$07E0          | FIRST PAIR OF DESCRIPTOR WORDS |

| DC.W  | \$13C8,\$0FF0          |                                |

| DC.W  | \$23C4,\$1FF8          |                                |

| DC.W  | \$13C8,\$0FF0          |                                |

| DC.W  | \$0990, <b>\$07</b> E0 |                                |

| DC.W  | \$0000,\$0000          | ;END OF SPRITE DATA            |

|       |                        |                                |

Add the following example to page 4-14, under section 4.3.1, "Selecting the Sprite DMA Channel and Setting the Pointers".

Initializing sprite data pointers:

; in this example the processor initializes the data pointers for sprite 0. ; Normally, this is done by the copper. The sprite is at address \$20000. ; SPR0PTH EQU \$DFF120 ;SPRITE 0 POINTER HIGH ORDER WORD SPR0PTL EQU \$DFF122 ;LOW ORDER WORD ; MOVE.L #\$20000,SPR0PTH ;WRITE \$20000 TO SPRITE 0 POINTER Add the following example to page 4-14 under Section 4.3, "Displaying a Sprite".

How to display a sprite:

```

This example displays the spaceship sprite at location V=65, H=128.

; The equates are the usual, so they're not repeated here.

; First, we set up a single bit plane.

POINT A0 AT CUSTOM CHIPS

LEA CUSTOM,A0

;1 BIT PLANE, COLOR IS ON

MOVE.W #$1200,BPLCON0(A0)

MOVE.W #$0000,BPL1MOD(A0)

:MODULO = 0

MOVE.W #$0000,BPLCON1(A0)

;HORIZONTAL SCROLL VALUE = 0

MOVE.W #$0024,BPLCON2(A0)

SPRITES HAVE PRIORITY OVER PLAYFIELDS

MOVE.W #$0038,DDFSTRT(A0)

SET DATA FETCH START

MOVE.W #$00D0,DDFSTOP(A0)

SET DATA FETCH STOP

MOVE.W #$2C81,DIWSTRT(A0)

SET DISPLAY WINDOW START

SET DISPLAY WINDOW STOP

MOVE.W #$F4C1,DIWSTOP(A0)

: Set up color registers

MOVE.W #$0008,COLOR00(A0)

BACKGROUND COLOR = DARK BLUE

MOVE.W #$0000,COLOR01(A0)

;FOREGROUND COLOR = BLACK

MOVE.W #$0FF0,COLOR17(A0)

;COLOR 17 = YELLOW

MOVE.W #$00FF,COLOR18(A0)

:COLOR 18 = CYAN

MOVE.W #$0F0F,COLOR19(A0)

; COLOR 19 = MAGENTA

; Move copper list to $20000

POINT A1 AT COPPER LIST DESTINATION

MOVE.L #$20000,A1

LEA COPPERL, A2

POINT A2 AT COPPER LIST SOURCE

;MOVE A LONG WORD

CLOOP: MOVE.L (A2),(A1)+

#$FFFFFFE,(A2)+ ;CHECK FOR END OF LIST

CMP.L

BNE CLOOP

LOOP UNTIL ENTIRE LIST IS MOVED

; Move sprite to $25000

POINT A1 AT SPRITE DESTINATION

MOVE.L #$25000,A1

LEA SPRITE,A2

POINT A2 AT SPRITE SOURCE

SPRLOOP:

;MOVE A LONG WORD

MOVE.L (A2)(A1)+

#$0000000,(A2)+

CHECK FOR END OF SPRITE

CMP.L

```

#### BNE SPRLOOP

#### ;LOOP UNTIL ENTIRE SPRITE IS MOVED

: Now we write a dummy sprite to \$30000, since all eight sprites are activated ; at the same time and we're only going to use one. The remaining sprites will point to this dummy sprite data. :WRITE IT MOVE.L #\$0000000,\$30000 ; Point copper at copper list MOVE.L #\$20000,CUSTOM+COP1LC ; Fill bitplane with \$FFFFFFF MOVE.L #\$21000,A1 POINT A1 AT BIT PLANE MOVE.W #2000,D0 :2000 LONG WORDS = 8000 BYTESMOVE.L **#**\$FFFFFFF,(A1)+ ;MOVE A LONG WORD OF \$FFFFFFFF FLOOP: ;DECREMENT COUNTER SUBQ.W #1,D0 **BNE FLOOP** LOOP UNTIL BITPLANE IS FULL : Start DMA MOVE.W CUSTOM+COPJMP1,D0 ;FORCE LOAD INTO COPPER ; PROGRAM COUNTER MOVE.W #\$83A0,(CUSTOM+DMACON) ;BITPLANE, COPPER, AND SPRITE DMA BRA ....next stuff to do... ; This is a copper list for one bit plane, and 8 sprites. The bit plane lives ; at \$21000. Sprite 0 lives at \$25000; all others live at \$30000 (the dummy ; sprite). COPPERL: DC.W \$00E0,\$0002 ;BIT PLANE 1 POINTER = \$21000\$00E2,\$1000 DC.W DC.W \$0120,\$0002 :SPRITE 0 POINTER = \$25000 \$0122,\$5000 DC.W SPRITE 1 POINTER = \$30000DC.W \$0124,\$0003 DC.W \$0126,\$0000 SPRITE 2 POINTER = \$30000DC.W \$0128,\$0003 DC.W \$012A,\$0000 DC.W SPRITE 3 POINTER = \$30000\$012C,\$0003

SPRITE 4 POINTER = \$30000

DC.W

DC.W

\$012E,\$0000

\$0130,\$0003

| DC.W                                                     | <b>\$0132,\$0000</b>                                             |                                        |

|----------------------------------------------------------|------------------------------------------------------------------|----------------------------------------|

| DC.W                                                     | \$0134,\$0003                                                    | ;SPRITE 5 POINTER = $30000$            |

| DC.W                                                     | <b>\$0136,<b>\$0000</b></b>                                      |                                        |

| DC.W                                                     | <b>\$0138,<b>\$00</b>03</b>                                      | ;SPRITE 6 POINTER = $30000$            |

| DC.W                                                     | \$013 <b>A</b> ,\$0000                                           |                                        |

| DC.W                                                     | <b>\$013C,\$0003</b>                                             | ;SPRITE 7 POINTER = $30000$            |

| DC.W                                                     | \$013E,\$0000                                                    |                                        |

| DC.W                                                     | \$FFFF,\$FFFE                                                    | END OF COPPER LIST                     |

| ,<br>· Sprite data fo                                    | r spaceship sprite.                                              | It appears on the screen at $V=65$ and |

| ; H=128.                                                 | I Spaceship Spires                                               |                                        |

| , <b>.</b>                                               |                                                                  |                                        |

| ; H=128.                                                 | \$6D60,\$7200                                                    | ;VSTART, HSTART, VSTOP                 |

| ; H=128.<br>;<br>SPRITE:                                 |                                                                  |                                        |

| ; H=128.<br>;<br>SPRITE:<br>DC.W                         | \$6D60,\$7200                                                    | ;VSTART, HSTART, VSTOP                 |

| ; H=128.<br>;<br>SPRITE:<br>DC.W<br>DC.W                 | \$6D60,\$7200<br>\$0990,\$07E0                                   | ;VSTART, HSTART, VSTOP                 |

| ; H=128.<br>;<br>SPRITE:<br>DC.W<br>DC.W<br>DC.W         | \$6D60,\$7200<br>\$0990,\$07E0<br>\$13C8,\$0FF0                  | ;VSTART, HSTART, VSTOP                 |

| ; H=128.<br>;<br>SPRITE:<br>DC.W<br>DC.W<br>DC.W<br>DC.W | \$6D60,\$7200<br>\$0990,\$07E0<br>\$13C8,\$0FF0<br>\$23C4,\$1FF8 | ;VSTART, HSTART, VSTOP                 |

Add the following example to page 4-15 under Section 4.4, "Moving a Sprite".

; This is an example of moving a sprite. We bounce the spaceship around : on the screen, making it change direction whenever it reaches an edge. : The sprite position data, containing VSTART and HSTART, lives in memory at \$25000. VSTOP is located at \$25002. We write to these locations to move the sprite. ; Once each frame, we increment (or decrement) VSTART by 1 and HSTART by 2. ; Then we calculate VSTOP which will be the new VSTART + 6. MOVE.B #151,D0 INITIALIZE HORIZONTAL COUNT MOVE.B #194,D1 ;INITIALIZE VERTICAL COUNT MOVE.B #64,D2 INITIALIZE HORIZONTAL POSITION MOVE.B #44,D3 INITIALIZE VERTICAL POSITION MOVE.B #1.D4 INITIALIZE HORIZONTAL INCREMENT VALUE: MOVE.B #1,D5 ;INITIALIZE VERTICAL INCREMENT VALUE ; Here we wait for the vertical blanking bit in INTREQR to turn on. This ; ensures a glitch free display. VLOOP: MOVE.W CUSTOM+INTREQR,D6 ;READ INTERRUPT REQUEST WORD AND.W #\$0020,D6 MASK OFF ALL BUT VERTICAL BLANK BIT BEQ VLOOP ;LOOP UNTIL BIT IS A 1 MOVE.W **#\$0020**,CUSTOM+INTREQ VERTICAL BIT IS ON, SO RESET IT. ; INCREMENT HORIZONTAL VALUE ADD.B D4.D2 #,D0 DECREMENT HORIZONTAL COUNTER SUBQ.B BNE L1 MOVE.B #151,D0 COUNT EXHAUSTED, RESET TO 151 EOR.B #\$FE,D4 NEGATE THE INCREMENT VALUE L1: MOVE.B D2,\$25001 WRITE NEW HSTART VALUE TO SPRITE ADD.B D5.D3 INCREMENT VERTICAL VALUE ;DECREMENT VERTICAL COUNTER SUBQ.B #1,D1 BNE L2 COUNT EXHAUSTED, RESET TO 194 MOVE.B #194.D1 EOR.B #\$FE,D5 ;NEGATE THE INCREMENT VALUE L2: MOVE.B D3,\$25000 WRITE NEW VSTART VALUE TO SPRITE MOVE.B D3,D6 ;MUST NOW CALCULATE NEW VSTOP ADD.B VSTOP ALWAYS VSTART+6 FOR SPACESHIP #6,D6 MOVE.B D6,\$25002 WRITE NEW VSTOP TO SPRITE **BRA VLOOP** :LOOP FOREVER.

Add the following example to page 4-18 under Section 4.6, "Reusing Sprite DMA Channels".

; This example displays the spaceship sprite and then redisplays it as a ; different object. I'm not going to tell you what it is, that's a secret. ; Only the sprite data list is affected by this, so that's all we'll show ; here. However, it looks best with the color registers set as follows: LEA CUSTOM.A0 MOVE.W **#**\$0F00,COLOR17(A0) ; COLOR 17 = REDMOVE.W **#**\$0FF0,COLOR18(A0) ; COLOR 18 = YELLOWMOVE.W **#**\$0FFF,COLOR19(A0) ; COLOR 19 = WHITE; And now for the sprite data. SPRITE: DC.W \$6D60,\$7200 DC.W \$0990,\$07E0 DC.W \$13C8,\$0FF0 DC.W \$23C4,\$1FF8 DC.W \$13C8,\$0FF0 DC.W \$0990,\$07E0 DC.W \$8080,\$8D00 VSTART, HSTART, VSTOP FOR NEW SPRITE DC.W \$1818,\$0000 DC.W \$7E7E,\$0000 DC.W \$7FFE,\$0000 DC.W **\$FFFF,\$2000** DC.W **\$FFFF,\$2000** DC.W **\$FFFF,\$3000** DC.W **\$FFFF,\$3000** DC.W \$7FFE,\$1800 DC.W \$7FFE,\$0C00 DC.W \$3FFC,\$0000 DC.W \$0FF0,\$0000 DC.W \$03C0,\$0000 \$0180,\$0000 DC.W DC.W \$0000,\$0000 ;END OF SPRITE DATA

Add the following example to page 4-23 under section 4.8, "Attached Sprites".

; The following data structure is for the six color spaceship made with two

; attached sprites.

SPRITE0:

| RIIEO.                   |                      |                                         |

|--------------------------|----------------------|-----------------------------------------|

| DC.W                     | \$6D60,\$7200        | ; VSTART = 65, HSTART = $128$           |

| DC.W                     | <b>\$0C30,\$0000</b> | FIRST COLOR DESCRIPTOR WORD             |

| DC.W                     | \$1818,\$0420        |                                         |

| DC.W                     | \$342C,\$0E70        |                                         |

| DC.W                     | \$1818,\$0420        |                                         |

| $\mathbf{DC}.\mathbf{W}$ | <b>\$0C30,\$0000</b> |                                         |

| DC.W                     | \$0000,\$0000        | ;END OF SPRITE 0                        |

| RITE1:                   |                      |                                         |

| DC.W                     | \$6D60,\$7280        | ;SAVE AS SPRITE 0 EXCEPT ATTACH BIT ON. |

| DC.W                     | \$07E0,\$0000        | FIRST DESCRIPTOR WORD FOR SPRITE 1      |

| DC.W                     | <b>\$0FF0,\$0000</b> |                                         |

|                          |                      |                                         |

| ,        |   |

|----------|---|

| SPRITE1: |   |

| DC \     | λ |

DC.W DC.W

DC.W

DC.W

\$1FF8,\$0000

**\$0FF0,\$0000** \$07E0,\$0000

\$0000,\$0000

;END OF SPRITE 1

## Addendum to Chapter 5: Audio Hardware

## Audio State Machine

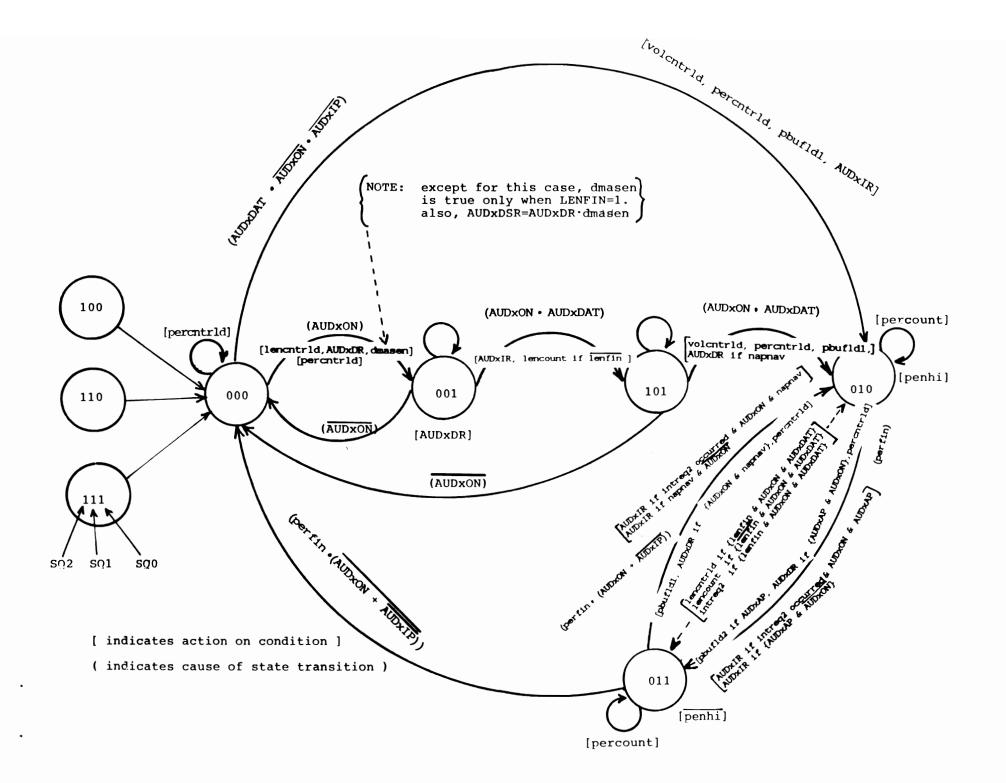

There is one audio state machine for each channel. See the attached state diagram. The machine has eight states and is clocked at the system clock frequency of 3.58 MHz. Three of the states are basically unused and just transfer back to the idle (000) state. One of the paths out of the idle state is designed for interrupt-driven operation (processor provides data), and the other path is designed for DMA-driven operation (Agnus provides data).

In interrupt-driven operation, transfer to the main loop (010,011 states) is immediate upon data written by the processor. In the 010 state the upper byte is output, and in the 011 state the lower byte is output. Transitions  $010\rightarrow011\rightarrow010$ ... occur whenever the period counter counts down to one. The period counter is reloaded at these transitions. As long as the interrupt is cleared by the processor in time, the machine remains in the main loop. Otherwise, it enters the idle state. Interrupts are generated on every word (011 $\rightarrow$ 010) transition.

In DMA-driven operation, transit to the 001 state occurs and DMA requests are sent to Agnus as soon as DMA is turned on. Because of pipelining in Agnus, the first data word must be thrown away. State 101 is entered as soon as this word arrives. A request for the next data word has already gone out. When the data arrives, state 010 is entered and the main loop continues until the DMA is turned off. The length counter counts down once with each word that comes in. When it finishes, a DMA restart request goes to Agnus along with the regular DMA request. This tells Agnus to reset the pointer to the beginning of the table of data. Also, the length counter is reloaded and an interrupt request goes out soon after the length counter finishes (counts to one). The request goes out just as the last word of the waveform starts its output.

DMA requests and restart requests are transferred to Agnus once each horizontal line, and the data comes back about 14 clock cycles (of 280ns) later.

In attach mode, things run a little differently. Attach volume has requests the same as normal operation (on the  $011\rightarrow010$ ) transition). In attach period, a set of requests occurs on the  $010\rightarrow011$  transition. With both attach period and attach volume high, requests occur on both transitions.

One of the consequences of the way this machine works is that if the sampling rate is set much higher than the normal max sampling rate (~29 kHz), the two samples in the buffer register will be repeated. If the filter on the Amiga is bypassed and the volume is set to max (40 hex), this feature can be used to make modulated carriers up to 1.79 MHz. The modulation is placed in the memory map, with plus values in the even bytes, and minus values in the odd bytes.

The following list shows the symbols used in the state diagram. Capitals are external signals; small letters are local signals.

| AUDxÓN     | DMA on "x" indicates channel number (signal from DMACON).                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------|

| AUDxIP     | Audio interrupt pending (input to channel from interrupt circuitry)                                                       |

| AUDxIR     | Audio interrupt request (output from channel to interrupt circuitry)                                                      |

| intreq1    | Interrupt request that combines with intreq2 to form AUDxIR                                                               |

| intreq2    | Prepare for interrupt request. Request comes out after the next $011 \rightarrow 010$ transition in normal operation.     |

| AUDxDAT    | Audio data load signal. Loads 16 bits of data to audio channel.                                                           |

| AUDxDR     | Audio DMA request to Agnus for one word of data.                                                                          |

| AUDxDSR    | Audio DMA request to Agnus to reset pointer to start of block                                                             |

| dmasen     | Restart request enable.                                                                                                   |

| percntrld  | Reload period counter from backup latch typically written by processor with AUDxPER (can also be written by attach mode). |

| percount   | Count period counter down one latch.                                                                                      |

| perfin     | Period counter finished (value $= 1$ ).                                                                                   |

| lencntrld  | Reload length counter from backup latch.                                                                                  |

| lencount   | Count length counter down one notch.                                                                                      |

| lenfin     | Length counter finished (value $= 1$ ).                                                                                   |

| volcntrld  | Reload volume counter from backup latch.                                                                                  |

| pbufld1    | Load output buffer from holding latch written to by AUDxDAT.                                                              |

| pbufld $2$ | Like pbufld1, but only during $010 \rightarrow 011$ with attach period.                                                   |

| AUDxAV     | Attach volume. Send data to volume latch of next channel instead of to $D \rightarrow A$ converter.                       |

.

AUDxAPAttach period. Send data to period latch of next channel instead of to the<br/>D $\rightarrow$ A converter.penhiEnable the high 8 bits of data to go to the D $\rightarrow$ A converter.napnav/AUDxAV \* /AUDxAP + AUDxAV—no attach stuff or else attach volume.

Condition for normal DMA and interrupt requests.

sq2,1,0 The name of the state flip-flops, MSB to LSB.

## Addendum to Chapter 6: Blitter Hardware

## Blitter Operations and System DMA

This section explains how the operation of the blitter affects the performance of the rest of the system. The section covers the following topics:

- o Blitter direct memory access (DMA) priority

- o DMA time slot allocation

- o Bus sharing between the 68000 and the bit-plane operations of the blitter and Copper.

- o Effects of different playfield display sizes on sprite display

- o Effects of blitter operation on the 68000's access to memory

## 1. Blitter DMA Priority

The blitter performs its various data fetch, modify, and store operations through a DMA sequence. It shares memory access with other devices in the system. In a system like the Amiga that uses a lot of DMA there must be some control over the priority of the accessing devices. A device's priority indicates its importance relative to other devices. The list below shows the order of priority for DMA operations, from highest priority to lowest.

- o Disk DMA-handles communications with the disk

- o Audio DMA-produces the sound

- o Bit-plane DMA produces the static display

- o Sprite DMA-produces the dynamic display

- o Copper-display-synchronized coprocessor

- o Blitter-data copying and line drawing device

o 68000 microprocessor — central processor

The first four devices in the list all have the same priority. If a disk DMA cycle is missed, some disk data is lost. If an audio cycle is missed, noise is added to the audio output. In displays (bitplane or sprite), there may be flashes or other interruptions on-screen. None of these situations are desirable and are avoided by making all of these devices priority 1. Under certain circumstances, however, the bit-plane DMA will take priority over sprite DMA.

Each of the first four devices in the list is specifically allocated a group of time slots during each horizontal scan of the video beam. If the device does not specifically request to use one of its allocated time slots, the slot is open for other uses.

The Copper has the next priority because it is designed as a display-synchronized coprocessor. It has to perform its operations at the same time during each display frame to remain synchronized with the display beam sweeping across the screen.

At the bottom of the list come the blitter and the 68000, in that order. The blitter is optimized for data copying, modifying, and line drawing operations. It performs these kinds of operations much faster than the 68000 could perform them. It is, therefore, given a higher priority than the processor so that it can do its job in the most efficient manner.

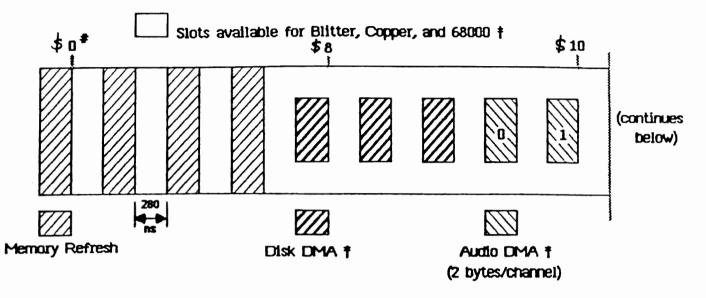

## 2. DMA Time Slot Allocation

During a horizontal scan line (about 63 microseconds), there are 227.5 "color-clocks". A color clock is the basic timing interval for memory access within this system and amounts to approximately 280 ns.

This interval of 227.5 color clocks includes both display time and non-display time on a horizontal line. Of this total time, there are 226 possible memory access cycles at 280 ns each to be allocated to the various devices that need memory access.

Each of the first four time slots in the list below is assigned at one of the odd-numbered slots available. This assignment was made to allow maximum bus utilization by the 68000 (as shown in the section titled "Bit-Plane/Processor Bus Sharing"). The even-numbered slots can be used by the Copper, blitter, or 68000.

Here is the time-slot allocation per horizontal line:

o 4 cycles for memory refresh

- o 3 cycles for disk DMA

- o 4 cycles for audio DMA (2 bytes per channel)

- o 16 cycles for sprite DMA (2 words per channel)

- o 80 cycles for bit-plane DMA (even and/or odd according to the display size used)

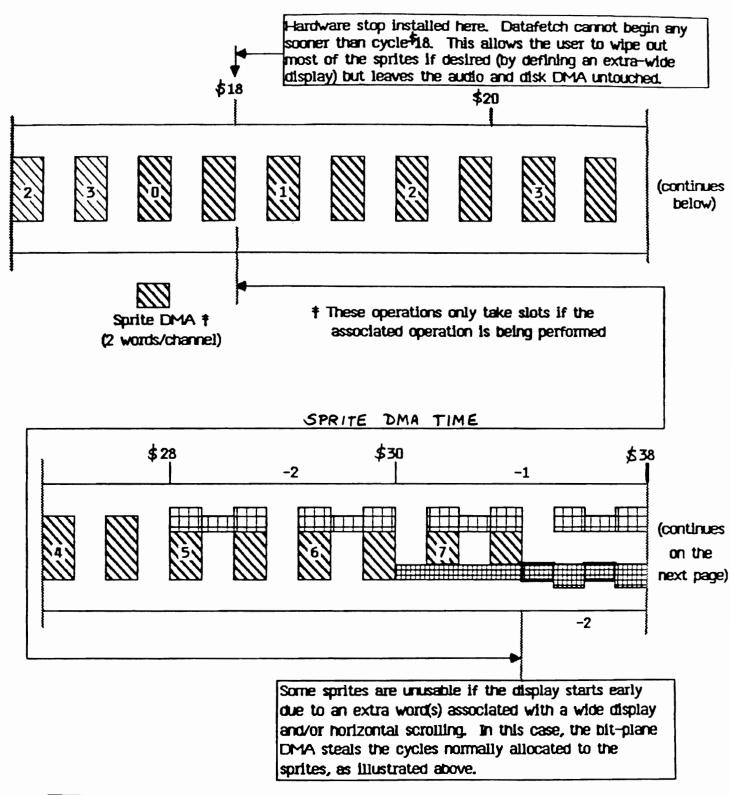

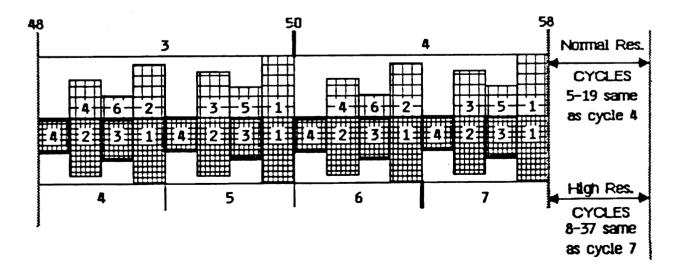

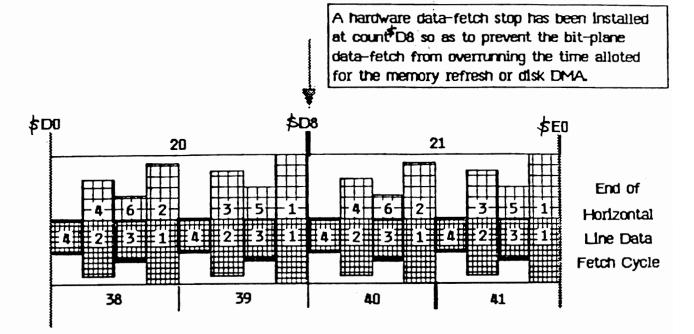

The figures on the following pages show one complete horizontal scan line and how the clock cycles are allocated.

# DMA Time Slot Allocation / Horizontal line

† These operations only take slots if the associated operation is being performed

Note: Copper Data Move instructions require 4 slots. Copper Wait instructions require 6 slots.

# This cycle 0 appears to exclude one of the memory refresh cycles. This is not the case.

Actual system hardware demands certain specific values for data fetch start and display start. Therefore this timing chart has been "adjusted" to match those requirements.

\$ Indicates a hex number.

Blitter 4

October 17, 1985

# DMA Time Slot Allocation / Horizontal line (cont'd)

320 mode Bit-Plane DMA, by plane †

640 mode Bit-Plane DMA, by plane †

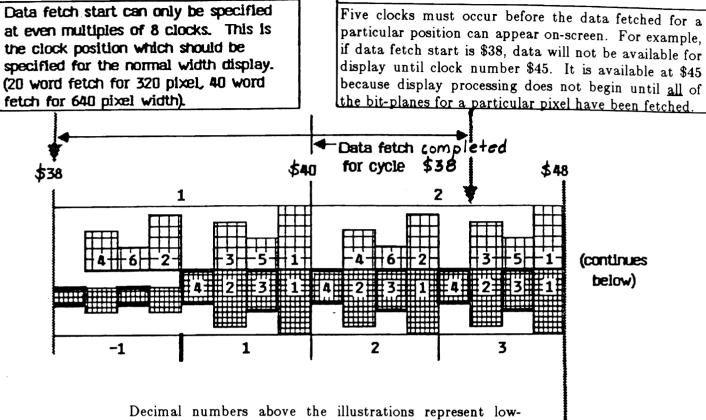

# DMA Time Slot Allocation / Horizontal line (cont'd)

Decimal numbers above the illustrations represent lowresolution cycles. Decimal numbers below the illustrations represent high-resolution cycles. Negative numbers indicate the start of data fetch for displays that are larger than normal.

Decimal numbers inside the illustrations represent the bitplane for which the data is being fetched.

# DMA Time Slot Allocation / Horizontal line (cont'd)

## 3. Bit-Plane/Processor Bus Sharing

The memory access cycles are interleaved to allow the 68000 processor to operate at close to its maximum speed. The 68000 spends about half of a complete processor instruction time doing internal operations and the other half accessing memory. Therefore, if the 68000 is given each alternate 280 ns memory cycle, it will appear to the 68000 that it has the memory all of the time and it will run at full speed.

Not all of the 68000 instructions allow this even-cycle allocation to mate perfectly all of the time. If it doesn't, the processor will have to wait until its next memory slot is available before continuing. Most 68000 instructions do not cause cycles to be missed, so it will run at full speed most of the time if there is no blitter DMA interference.

The following figure illustrates the normal cycle of the 68000.

| <> average 68000 cycle>                           |                                                                |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| <><br>operation<br>portion                        | <><br>access<br>portion                                        |  |  |  |  |  |  |  |  |  |

| odd cycle<br>number, assigned<br>to other devices | even cycle,<br>possibly used<br>by 68000 if it<br>requested it |  |  |  |  |  |  |  |  |  |

If there are 4 or less low-resolution bit-planes, then the 68000 can be granted each alternate memory cycle (if it is ready to ask for the cycle and is the highest priority item at the time). However, if there are more than 4 bit-planes, the bit-plane DMA will begin to steal cycles from the 68000 during the display time.

The following figure illustrates the time slots (each 280 ns) that will be taken by bit-plane DMA during the display time (160 slots out of 227 for each horizontal line for a 320-pixel, low-resolution display) for a 6-bit-plane display. As you will see from the figure, the bit-plane steals 50% of the open slots that the processor might have used if there were only 4 bit-planes displayed.

| Т |   | - | T+7 |   |   |   |   |  |  |

|---|---|---|-----|---|---|---|---|--|--|

| + |   | * |     | + |   | * |   |  |  |

|   | 4 | 6 | 2   |   | 3 | 5 | 1 |  |  |

- + an open memory slot that the 68000 might use

- \* a slot that cannot be used by the 68000 due to added bit-plane DMA

If you specify 4 high-resolution bit-planes (640 pixels wide), bit-plane DMA needs all of the available memory time slots during the display time just to grab the 40 data words for each line of the 4 bit-planes (40 X 4 = 160 time slots). This effectively locks out the 68000 (as well as the blitter or Copper) from any memory access during the actual period of the display.

The following figure shows how the time slots are allocated for high-resolution bit-planes.

| Т |   | - timing cycle - |   |   |   |   |   |  |  |

|---|---|------------------|---|---|---|---|---|--|--|

| 4 | 2 | 3                | 1 | 4 | 2 | 3 | 1 |  |  |

## 4. Effects of Different Display Sizes

The normal, full-sized screen consists of 320 pixels for low-resolution mode or 640 pixels for highresolution mode. This means that either 20 or 40 words will be fetched during the horizontal line display time.

When you want to scroll either or both playfields, one extra data word per line must be fetched from the memory. This extra word provides the pixels that will show on-screen as scrolling occurs.

Screen size is adjustable (see the descriptions of DIWSTRT, DIWSTOP, and DDFSTRT in Chapter 3, "Playfield Hardware". Bit-plane DMA takes precedence over sprite DMA. Therefore, larger screens may block out one or more of the highest-numbered sprites, especially with scrolling.

## 5. Effects of Blitter Operation

As mentioned above, the blitter normally has a higher priority than the processor for DMA cycles. There are certain cases, however, where the blitter and the 68000 will share memory cycles. The blitter uses every cycle. If given the chance, it would steal every available memory cycle. Display, disk, and audio DMA take precedence, so the blitter cannot block them from bus access. Depending on the state of the setting of the blitter DMA mode bit, commonly referred to as the "blitter-nasty" bit, the processor may not be so lucky. This bit is called BLTPRI (for "blitter has priority over processor") and is in register DMACONW.

If BLTPRI is a 1, the blitter will hang onto the bus for every available memory cycle. In the nondisplay time (horizontal blanking interval), this could potentially be every single cycle. Even in blitter-nasty mode, there may be cases when you can grant a few cycles to the 68000. Even though the blitter would seem to be acting as a bus-hog, there are data windows that occur during certain blitter operations when the blitter is doing something internally rather than on the bus. These cycles are part of the basic operating sequence of the blitter itself.

If BLTPRI is a 0, the DMA manager will monitor the 68000 cycle requests. If the 68000 is unsatisfied for three consecutive memory cycles, the blitter will release the bus for 1 cycle.

The DMA manager knows when these cycles of the blitter are about to occur and will release them to the 68000 if it is waiting for memory access. Blitter-nasty mode doesn't *prevent* the 68000 from executing instructions, but it surely slows it down.

Table 1 shows all of the possible operating modes of the blitter along with the distribution of the memory access windows within its operation. The table shows three words of a blit (the first, any middle, and the last) and how the bus activity occurs for this sequence. The following conventions are used:

- o A, B, and C stand for the sources.

- o D stands for the destination.

- o A0 is the first memory word fetch; A1 is any middle memory word fetch; A2 is the last memory word fetch.

- An asterisk (\*) following a source name indicates an internal cycle used for that source; the cycle does no data fetch. For these functions, the cycle fetch columns have blank spaces that indicate open memory cycles where some other device can access the bus. Thus functions such as item 3, ABC\*->D can be read as AB->D.

- o Z stands for a no-data-stored case (no destination).

- o (f) stands for fill and (n) stands for no-fill, if the use of fill makes a difference.

Table 1: Blitter Memory Bus Activity

| (            | Operation Type |            | N             | <i>A</i> emo | ry Cy      | ycle [     | )ata ]     | Fetch     | or D       | ata S | store | Usag | e  |    |

|--------------|----------------|------------|---------------|--------------|------------|------------|------------|-----------|------------|-------|-------|------|----|----|

| 1.           | АВСD           | <b>A0</b>  | <b>B0</b>     | C0           |            | <b>A</b> 1 | <b>B</b> 1 | C1        | D0         | A2    | B2    | C2   | D1 | D2 |

| <b>2</b> .   | АВСZ           | <b>A0</b>  | <b>B0</b>     | <b>C0</b>    | <b>A1</b>  | <b>B1</b>  | C1         | A2        | <b>B2</b>  | C2    |       |      |    |    |

| 3.           | A B C*D(f)     | <b>A0</b>  | <b>B0</b>     |              |            | <b>A1</b>  | <b>B</b> 1 | D0        |            | A2    | B2    | D1   |    | D2 |

| <b>4</b> .   | A B C*D(n)     | <b>A0</b>  | <b>B0</b>     | <b>A</b> 1   | <b>B</b> 1 | D0         |            | A2        | <b>B</b> 2 | D1    |       | D2   |    |    |

| <b>5</b> .   | A B C*Z        | <b>A0</b>  | <b>B0</b>     |              | <b>A</b> 1 | <b>B1</b>  |            | A2        | B2         |       |       |      |    |    |

| <b>6</b> .   | A CD           | <b>A</b> 0 | <b>C0</b>     |              | <b>A1</b>  | C1         | D0         | A2        | C2         | D1    |       | D2   |    |    |

| 7.           | A CZ           | <b>A0</b>  | <b>C0</b>     | <b>A1</b>    | C1         | A2         | C2         |           |            |       |       |      |    |    |

| 8.           | A C*D(f)       | <b>A0</b>  |               |              | <b>A1</b>  | D0         | A2         | D1        |            | D2    |       |      |    |    |

| 9.           | A C*D(n)       | <b>A0</b>  |               | A1           | D0         | A2         | D1         |           | D2         |       |       |      |    |    |

| 10.          | A C*Z          | <b>A</b> 0 |               | <b>A1</b>    |            | A2         |            |           |            |       |       |      |    |    |

| 11.          | A* B C D       |            | BO            | <b>C0</b>    |            |            | B1         | <b>C1</b> | D0         |       | B2    | C2   | D1 | D2 |

| 1 <b>2</b> . | A* B CZ        |            | <b>B</b> 0    | <b>C0</b>    |            | B1         | C1         |           | <b>B2</b>  | C2    |       |      |    |    |

| 13.          | A* B C* D(f)   |            | <b>B0</b>     |              |            |            | <b>B</b> 1 | D0        |            |       | B2    | D1   |    | D2 |

| 14.          | A* B C*D(n)    |            | <b>B0</b>     |              |            | <b>B</b> 1 | D0         |           | B2         | D1    |       | D2   |    |    |

| 15.          | A* B C*Z       |            | <b>B</b> 0    |              |            | <b>B</b> 1 |            |           | <b>B2</b>  |       |       |      |    |    |

| 16.          | A* CD          |            | $\mathbf{C0}$ |              |            | C1         | D0         |           | C2         | D1    |       | D2   |    |    |

| 17.          | A* CZ          |            | C0            |              | C1         |            | C2         |           |            |       |       |      |    |    |

| 18.          | A* C*D(f)      |            |               |              |            | D0         |            |           | D1         |       |       | D2   |    |    |

| 19.          | A* C*D(n)      |            |               |              | D0         |            | D1         |           | D2         |       |       |      |    |    |

| <b>20</b> .  | A* C*Z         |            |               |              |            |            |            |           |            |       |       |      |    |    |

| 21.          | LINE DRAWING   |            |               |              |            |            |            |           |            |       |       |      |    |    |

|              | MODE           |            | C0            | *            | D0         |            | C1         | *         | D1         |       | C2    | *    | D2 |    |

Notes for Table 1:

- a. Function 9 is a block move only when both shift values are 0. Use function 14 if either shift value is nonzero.

- b. Function 10 is a zero test; function 19 is a constant fill.

- c. Function 21 is for line drawing. The cycles marked with \* are not used by the blitter but are not released to the system. Sorry.

d. Functions 11, 13, 14, and 16 have special restraints when source and data overlap. During some priority overrides, the order of data fetch and store will be reversed. When using these functions with overlapping source and data, the overlap must be greater than two words. Otherwise, you risk overwriting your source data.

### APPENDIX F - Amiga Hardware Manual

This appendix contains information about the 8520 peripheral interface adapters.

\*\*\*\*\*\*\*\*\*\*\*

### QUICK REFERENCE

### BRIEF ADDRESS MAP FOR 8520'S

The system hardware selects the 8520's (aka CIA's) when the upper three address bits are 101.

Furthermore, CIAA is selected when A12 is low, A13 high; CIAB is selected when A12 is high, A13 low.

You can use either byte or word addresses to access the 8520's. For byte access (seems to be the usual case), A0 must be 0 for CIAA, 1 for CIAB. For word access, CIAB communicates on data bits 15"8; CIAA communicates on data bits 7"0. (A0 is always 0 for word access, naturally).

Address bits All, Al0, A9, and A8 are used to specify which of the 16 internal registers you want to access. This is indicated by "r" in the address.

All other bits are don't cares. So, CIAA is selected by the following binary address: 101x xxxx xx01 rrrr xxxx xxx0. CIAB address: 101x xxxx xx10 rrrr xxxx xxx1

With future expansion in mind, we have decided on the following addresses: CIAA = BFEr01; CIAB = BFDr00.

### CIAB Address Map

|                                                                                                                                                              | Register<br>Name | 7                                                                                                              | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                                                                                      | Data b<br>4                                                 |                                                     | 2                                                              | 1                                       | 0    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------|-----------------------------------------|------|

| BFD000<br>BFD100<br>BFD200<br>BFD300<br>BFD400<br>BFD500<br>BFD600<br>BFD700<br>BFD800<br>BFD900<br>BFDA00<br>BFDB00<br>BFDD00<br>BFDD00<br>BFDD00<br>BFDE00 |                  | /DTR<br>/MTR<br>ddr fo<br>ddr fo<br>CIAB<br>CIAB<br>CIAB<br>CIAB<br>Horizo<br>Horizo<br>not us<br>CIAB<br>CIAB | /RTS<br>/SEL3<br>or port<br>or port<br>fimer 1<br>fimer 1<br>fim | /CD<br>/SEL2<br>t A (B<br>t B (B<br>A low<br>A high<br>B low<br>B high<br>sync e<br>sync e<br>sync e<br>data<br>upt co | /CTS<br>/SEL1<br>FD000);<br>FD100);<br>byte<br>byte<br>byte | /DSR<br>/SEL0<br>1 = 0<br>1 = 0<br>ounter<br>ounter | SEL<br>/SIDE<br>output<br>output<br>bits 7<br>bits 1<br>bits 2 | POUT<br>DIR<br>(set t<br>(set t<br>.5~8 | BUSY |

| BEDE00                                                                                                                                                       |                  | CIAB                                                                                                           | Contro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | l regi                                                                                                                 | ster B                                                      |                                                     |                                                                |                                         |      |

Note: CIAB can generate INT6.

CIAA Address Map

.

.

| Byte             | Register |                     |                          | Data                 | bits          |        |      |          |      |

|------------------|----------|---------------------|--------------------------|----------------------|---------------|--------|------|----------|------|

| Address          | Name     | 7                   | 6 5<br>                  | 4                    | 3             | 2      | 1    | 0        |      |

| BFE001           |          | IR1 /F<br>arallel   |                          | Y /TK0               | /WPRO         | /CHING | /LED | OVL      |      |

| BFE101<br>BFE201 | do       | ir for              | port A                   | (BFE001)             | ; 1 = 0       | output | (Set | to 0x03) |      |

| BFE301<br>BFE401 | do<br>Cl | ir for j<br>[AA Tim | port B<br>er <b>A</b> lo | (BFE101)<br>w byte   | ; 1 = 0       | output | (Can | be in or | out) |

| BFE501           |          |                     | er A hi<br>er B lo       | gh byte              |               |        |      |          |      |

| BFE601<br>BFE701 | CI       | AA Tim              | er B hi                  | gh byte              |               |        |      |          |      |

| BFE801<br>BFE901 |          |                     |                          | nter bit<br>nter bit |               |        |      |          |      |

| BFEA01<br>BFEB01 |          | ) Hz ev<br>ot used  |                          | nter bit             | <b>s 23~1</b> | 5      |      |          |      |

| BFEC01           | CI       | AA Ser              | ial dat                  | a regist             |               |        | )    |          |      |

| BFED01<br>BFEE01 |          |                     |                          | control<br>gister A  |               | er     |      |          |      |

| BFEF01           | CI       | AA Con              | trol re                  | gister E             | 5             |        |      |          |      |

Note: CIAA can generate INT2.

\*\*\*\*\*

INTERFACE SIGNALS

Clock Input

The 02 clock is a TTL compatible input used for internal device operation and as a timing reference for communicating with the system data bus.

CS - Chip Select Input

The CS input controls the activity of the 8520. A low level on CS while 02 is high causes the device to respond to signals on the R/W and address (RS) lines. A high on CS prevents these lines from controlling the 8520. The CS line is normally activated (low) at 02 by the appropriate address combination.

R/W - Read/Write Input

The R/W signal is normally supplied by the microprocessor and controls the direction of data transfers of the 8520. A high on R/W indicates a read (data transfer out of the 8520), while a low indicates a write (data transfer into the 8520).

RS3-RS0 - Address Inputs

The address inputs select the internal registers as described by the Register Map.

DB7-DB0 - Data Bus Inputs/Outputs

The eight data bus output pins transfer information between the 8520 and the system data bus. These pins are high impedance inputs unless CS is low and R/W and 02 are high, to read the device. During this read, the data bus output buffers are enabled, driving the data from the selected register onto the system data bus.

IRQ - Interrupt Request Output

IRQ is an open drain output normally connected to the processor interrupt input. An external pull-up resistor holds the signal high, allowing multiple IRQ outputs to be connected together. The IRQ output is normally off (high impedance) and is activated low as indicated in the functional description.

RES - Reset Input

A low on the RES pin resets all internal registers. The port pins are set as inputs and port registers to zero (although a read of the ports will return all highs because of passive pull-ups). the timer control registers are set to zero and the timer latches to all ones. All other registers are reset to zero.

REGISTER MAP

-----

Each 8520 has 16 registers which you may read or write. Here is the list of registers and the access address of each within the memory space dedicated to the 8520:

|     |     |     |     | Register | -    |                            |

|-----|-----|-----|-----|----------|------|----------------------------|

| RS3 | RS2 | RS1 | RS0 | # (hex)  | NAME | MEANING                    |

| 0   | 0   | 0   | 0   | 0        | PRA  | Peripheral Data Register A |

| 0   | 0   | 0   | 1   | 1        | PRB  | Peripheral Data Register B |

| 0   | 0   | 1   | 0   | 2        | DDRA | Data Direction Register A  |

| 0   | 0   | 1   | 1   | 3        | DDRB | Direction Register B       |

| 0   | 1   | 0   | 0   | 4        | TALO | Timer A Low register       |

| 0   | 1   | 0   | 1   | 5        | TAHI | Timer A High register      |

| 0   | 1   | 1   | 0   | 6        | TBLO | Timer B Low register       |

| 0   | 1   | 1   | 1   | 7        | TBHI | Timer B High register      |

| 1   | 0   | 0   | 0   | 8        |      | Event LSB                  |

| 1   | 0   | 0   | 1   | 9        |      | Event 8-15                 |

| 1   | 0   | 1   | 0   | Α        |      | Event MSB                  |

| 1   | 0   | 1   | 1   | В        |      | No Connect                 |

| Oct 15 17:15 1985 Appendix_F Page 4                                                                                                                                                                                                                                                                                                                                                           |   |  |  |  |  |  |  |  |  |  |  |