### The Blacksburg Continuing Education<sup>™</sup> Series

The Blacksburg Continuing Education Series<sup>™</sup> of books provide a Laboratory—or experimentoriented approach to electronic topics. Present and forthcoming titles in this series include:

- Circuit Design Problems for the TRS-80

- DBUG: An 8080 Interpretive Debugger

- Design of Active Filters, With Experiments

- Design of Op-Amp Circuits, With Experiments

- Design of Phase-Locked Loop Circuits, With Experiments

- Design of Transistor Circuits, With Experiments

- Design of VMOS Circuits, With Experiments

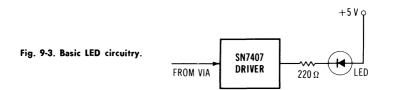

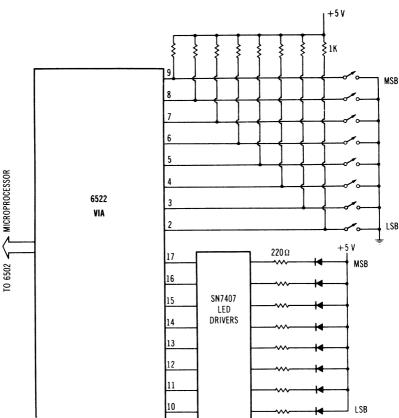

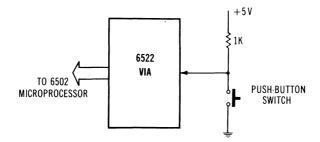

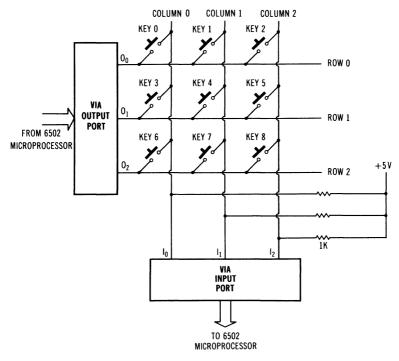

- The 8080A Bugbook<sup>®</sup>: Microcomputer Interfacing and Programming

- 8080/8085 Software Design (2 Volumes)

- 8085A Cookbook

- 555 Timer Applications Sourcebook, With Experiments

- Guide to CMOS Basics, Circuits, & Experiments

- How to Program and Interface the 6800

- Interfacing and Scientific Data Communications Experiments

- Introductory Experiments in Digital Electronics and 8080A Microcomputer Programming and Interfacing (2 Volumes)

- Logic & Memory Experiments Using TTL Integrated Circuits (2 Volumes)

- Microcomputer—Analog Converter Software and Hardware Interfacing

- Microcomputer Interfacing With the 8255 PPI Chip

- NCR Basic Electronics Course, With Experiments

- NCR Data Communications Concepts

- NCR Data Processing Concepts Course

- NCR EDP Concepts Course

- Programming and Interfacing the 6502, With Experiments

- 6801, 68701, and 6803 Microcomputer Programming and Interfacing

- 6502 Software Design

- TEA: An 8080/8085 Co-Resident Editor/Assembler

- TRS-80 Interfacing (2 Volumes)

- Z-80 Microprocessor Programming & Interfacing (2 Volumes)

In most cases, these books provide both text material and experiments, which permit one to demonstrate and explore the concepts that are covered in the book. These books remain among the very few that provide step-by-step instructions concerning how to learn basic electronic concepts, wire actual circuits, test microcomputer interfaces, and program computers based on popular microprocessor chips. We have found that the books are very useful to the electronic novice who desires to join the "electronics revolution," with minimum time and effort.

Additional information about the "Blacksburg Group" is presented inside the rear cover.

Jonathan A. Titus, Christopher A. Titus, and David G. Larsen "The Blacksburg Group"

Bug symbol trademark Nanotran, Inc., Blacksburg, VA 24060 Bugbook is a registered Trademark of E & L Instruments, Inc., Derby, CT 06418

# 6502 Software Design

,

By Leo J. Scanlon

Howard W. Sams & Co., Inc. 4300 WEST 62ND ST. INDIANA POLIS, INDIANA 46268 USA Copyright © 1980 by Leo J. Scanlon

#### FIRST EDITION SECOND PRINTING-1980

All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission from the publisher. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 0-672-21656-6 Library of Congress Catalog Card Number: 79-67131

Printed in the United States of America.

## Preface

The 6502 integrated circuit is a very popular microprocessor. It is currently used in general-purpose microcomputers, video games, and personal computers such as the Apple and the Pet 2001. Many of these microcomputers are programmed in the BASIC\* programming language, which makes it very easy to write programs that will perform complex calculations or play games. However, the BASIC language also has its disadvantages. It is relatively slow (only a few hundred statements can be executed every second) and it is not very suitable for controlling peripheral devices. Therefore, if you have a high-speed data-processing or peripheral-control requirement, assembly language programs will probably have to be written.

Once you have decided that assembly language is the language to use, you will need a 6502-based microcomputer that you can use to generate and test your programs. The microcomputer that has been used as the basis for this book is the AIM 65. It is manufactured by Rockwell International. The AIM 65 has a 54-key keyboard, a 20-character alphanumeric LED display, a 20-column thermal printer, a teletypewriter I/O port and two audio cassette I/O ports. As such, it is a very powerful, inexpensive microcomputer system. Even though we have used this microcomputer in our examples, most of the programs listed in this book can be used on all 6502based microcomputers. However, they may have to be slightly altered to reflect the memory and I/O devices that are wired to your microcomputer.

This book has nine chapters. Chapter 1 discusses the characteristics of the 6502 integrated circuit and the AIM 65 microcomputer.

<sup>\*</sup>BASIC is a registered trademark of the trustees of Dartmouth College.

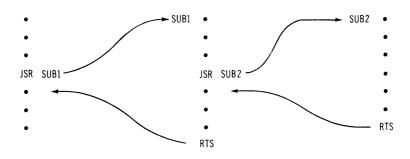

This includes a description of the various *registers* contained within the 6502 integrated circuit. These registers are important because you will use them time and time again in your programming. Chapter 2 presents descriptions of the instructions that the 6502 integrated circuit can actually execute. However, you will not find long detailed programs in this chapter, since you will not have enough familiarity with all of the important instructions to understand long complex programs. Then, Chapter 3 discusses subroutines, which are instruction sequences that are designed to be used at several places in a program.

Chapters 4 through 6 present techniques needed to process structured data (such as lists and tables), perform mathematical operations, and convert data from one number base to another. Finally, Chapters 7 through 9 describe how the 6502 instructions can be used to transfer information between the 6502 integrated circuit and the peripheral input/output devices.

This chapter arrangement, starting with very fundamental material and gradually introducing more complex topics, is intended to increase your understanding of the 6502 integrated circuit in an *orderly* manner.

LEO J. SCANLON

This book is dedicated to my wife, Pat, and my sons, Roger and Ryan.

## Acknowledgments

On a personal note, it is only proper to mention that although the only name on the title page is that of the author, this book reflects the efforts of many people. In particular, the author is indebted to Dr. Christopher A. Titus of Tychon, Inc., the editor (and reader's advocate) for this book, for his keen insight and many constructive suggestions. Special thanks must also go to Dr. Lance A. Leventhal of Emulative Systems, who gave of his valuable time with infectious enthusiasm. Finally, the author owes thanks to many dedicated people at Rockwell International in Anaheim, California, with particular appreciation for the management support of Bob Anslow and Scotty Maxwell and the technical contributions of Gordon Smith, Dick Anderson and Leo Pardo.

## Contents

| LIST OF PROGRAM EXAMPLES |  |  |  |  |  |  |  |  |  |  | 9 |

|--------------------------|--|--|--|--|--|--|--|--|--|--|---|

|--------------------------|--|--|--|--|--|--|--|--|--|--|---|

#### CHAPTER 1

Why the 6502?-The 6502 Microprocessor-Machine Code and Assembly Language-The AIM 65 Microcomputer-Conventions Used in This Book-References

#### **CHAPTER 2**

| Тне 6502 М | ICROPROCESSOR  | INSTRUCTION | Set . |   |  |  | 27   | 1 |

|------------|----------------|-------------|-------|---|--|--|------|---|

|            | IONOT NOOLDOON | momon       |       | • |  |  | - 41 |   |

Summary of the Instruction Set-How This Chapter Is Arranged-6502 Addressing Modes-Load and Store Instructions-Arithmetic Instructions – Increment and Decrement Instructions – Logical Instructions-Jump, Branch, Compare, and Bit-Test Instructions-Shift and Rotate Instructions-Register Transfer Instructions-Stack Instructions-The No Operation Instruction-Summary

#### **CHAPTER 3**

SUBROUTINES . .

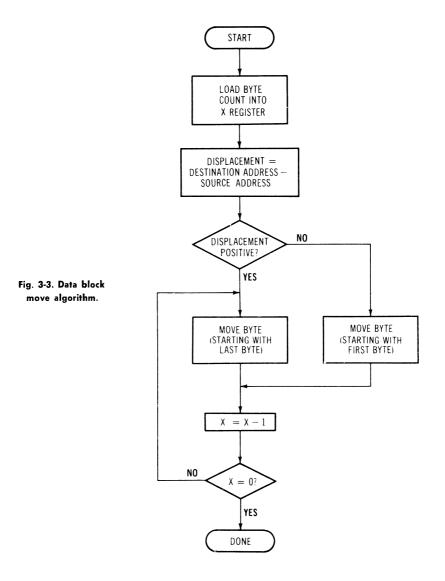

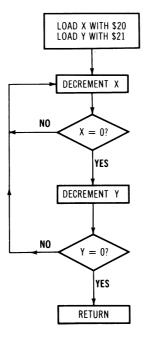

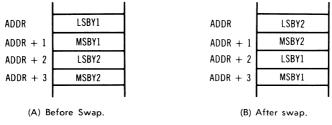

Subroutine Instructions-Subroutine Nesting-Moving Data in Memory-Time-Delay Subroutines-Summary 75

#### **CHAPTER 4**

| LISTS AND LOOK-UP TABLES                              | • | • | • | •   | •   | •   | •    | •     | •    | •    | • | 92 |

|-------------------------------------------------------|---|---|---|-----|-----|-----|------|-------|------|------|---|----|

| Unordered Lists–A Simple 3<br>Up Tables–Jump Tables–F |   | - |   | miq | ue- | Ord | ered | l Lis | ts—I | Look | - |    |

#### **CHAPTER 5**

| MATHEMATICAL | Routines |  | • |  | • | • | • | 114 |

|--------------|----------|--|---|--|---|---|---|-----|

|              |          |  |   |  |   |   |   |     |

Integer Addition – Integer Subtraction – Integer Multiplication – Integer Division–BCD Mathematics–Floating-Point Mathematics– Square Root

#### **CHAPTER 6**

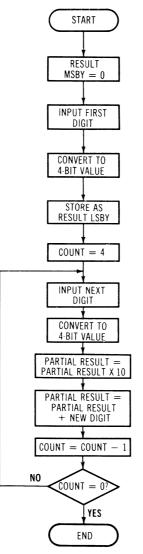

Two Simple I/O Devices-Two-Digit ASCII-Based Hexadecimal-to-Binary Conversion-An 8-Bit Binary-to-ASCII-Based Hexadecimal Conversion-Three-Digit ASCII-Based Decimal-to-Binary Conversion - Five-Digit ASCII-Based Decimal-to-Binary Conversion - An 8-Bit Binary-to-ASCII-Based Decimal Conversion - A 16-Bit Binary-to-ASCII-Based Decimal Conversion-Two-Digit ASCII-Based Decimalto-BCD Conversion-Two-Digit BCD-to-ASCII-Based Decimal Conversion-Leading Zero Suppression-Summary

#### CHAPTER 7

The 6502 Microprocessor Interrupts-Interrupt Request  $(\overline{IRQ})$ -Return From Interrupt (RTI) Instruction-Summary of IRQ-Generated Interrupts-Nonmaskable Interrupt  $(\overline{NMI})$ -The Break (BRK) Instruction-AIM 65 Breakpoints-Reset Considerations-Summary-References

#### **CHAPTER 8**

The 6520 Peripheral Interface Adapter (PIA)-PIA Register Addressing-PIA Control Registers-Configuring the PIA-Data Transfers Using a PIA-The 6522 Versatile Interface Adapter (VIA)-VIA Register Addressing-Parallel Data Transfers Using a VIA-VIA

#### 6502 SOFTWARE DESIGN

Peripheral Control Register (PCR)-VIA Interrupt Requests-VIA Auxiliary Control Register (ACR)-VIA Timers-A 24-Hour Clock for the AIM 65-VIA Shift Register-References

#### CHAPTER 9

| MICROCOMPUTER INPUT/OUTPUT                                                                                                                                                                                                             |               |               |           | 219 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|-----------|-----|

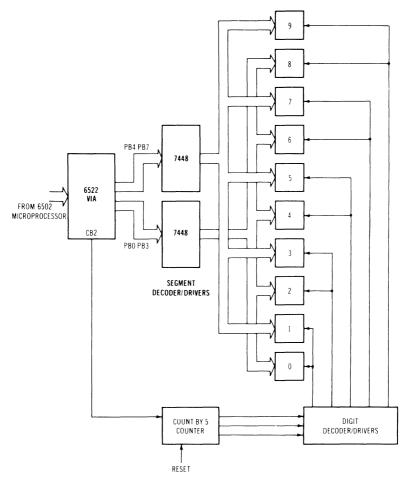

| The 6502 Microprocessor and Simple I/O Devices—Ano<br>Input Device—The 6502 Microprocessor and Keyboards—<br>Keyboards—Encoded Keyboards—Interfacing With Tele<br>—The 6502 Microprocessor and Seven-Segment LED<br>Summary—References | Une:<br>etype | ncod<br>write | ed<br>ers |     |

|                                                                                                                                                                                                                                        | Dis           | plays         | 5         |     |

#### APPENDIX A

| ASCII CHARACTER SET (7-BIT CODE) |  |  |  |  |  |  |  | 244 |

|----------------------------------|--|--|--|--|--|--|--|-----|

|----------------------------------|--|--|--|--|--|--|--|-----|

#### APPENDIX B

| Summary | OF | THE | 6502 | Inst | RUC | TION | Set | • | • | • |  | • | 245 |

|---------|----|-----|------|------|-----|------|-----|---|---|---|--|---|-----|

| Index . |    | •   |      |      |     |      |     |   | • |   |  |   | 265 |

# List of Program Examples

#### CHAPTER 1

| 1-1 | A Typical 6 | 3502 | Pro | ogra | ım, | in | Bina | ary | and | H | exa | dec | ima | ıl |    |

|-----|-------------|------|-----|------|-----|----|------|-----|-----|---|-----|-----|-----|----|----|

|     | Notation    | •    | •   | •    | •   | •  | •    | •   | •   | • | •   | •   | •   | •  | 22 |

#### **CHAPTER 2**

| 2-1  | A Double-Precision Addition Routine          |     |   |  | 46 |

|------|----------------------------------------------|-----|---|--|----|

| 2-2  | A Double-Precision Subtraction Routine .     |     |   |  | 47 |

| 2-3  | A Six-Byte Memory Move Routine               |     |   |  | 49 |

| 2-4  | Testing Two Locations for Equality           |     |   |  | 60 |

| 2-5  | Arranging Two Numbers in Order of Value      |     |   |  | 60 |

| 2-6  | A Three-Way Decision Routine                 |     |   |  | 60 |

| 2-7  | A Multiple-Byte Move Routine                 |     |   |  | 61 |

| 2-8  | Waiting for a Memory Bit to Become Logic (   | )   |   |  | 62 |

| 2-9  | Waiting for Any of Three Memory Bits to Bed  | com | e |  |    |

|      |                                              |     |   |  | 63 |

| 2-10 | A Left-Shift Routine for Multiple-Precision  |     |   |  |    |

|      | Unsigned Numbers                             |     |   |  | 67 |

| 2-11 | A Left-Shift Routine for Multiple-Precision  |     |   |  |    |

|      | Signed Numbers                               |     | • |  | 67 |

| 2-12 | A Right-Shift Routine for Multiple-Precision |     |   |  |    |

|      | Signed Numbers                               |     |   |  | 69 |

| 2-13 | Accessing Nonconsecutive Elements in a List  |     |   |  | 69 |

| 2-14 | Initializing the Stack Pointer to \$FF       |     |   |  | 71 |

| 2-15 | Saving All Registers on the Stack            |     |   |  | 73 |

|      | 0 0                                          |     |   |  |    |

#### 6502 SOFTWARE DESIGN

#### CHAPTER 3

| 3-1 | The Subroutine Call and Return Sequence .    |     |  | 78 |

|-----|----------------------------------------------|-----|--|----|

| 3-2 | Subroutine Nesting                           |     |  | 80 |

| 3-3 | A Data-Block Move Subroutine                 |     |  |    |

| 3-4 | A Time-Delay Subroutine                      |     |  | 85 |

| 3-5 | A 30-Second Time-Delay Subroutine            |     |  | 88 |

| 3-6 | A Simplified 30-Second Time-Delay Subroutine |     |  | 89 |

| 3-7 | A One-Minute Time-Delay Subroutine           |     |  | 89 |

| 3-8 | A One-Hour Time-Delay Subroutine That Calls  | the |  |    |

|     | ONEMIN Subroutine                            |     |  | 90 |

|     |                                              |     |  |    |

#### **CHAPTER 4**

| 4-1  | Adding an Entry to an Unordered List         |          |  | 93  |

|------|----------------------------------------------|----------|--|-----|

| 4-2  | Deleting an Entry From an Unordered List .   |          |  | 95  |

| 4-3  | Find the Minimum and Maximum Values in an    |          |  |     |

|      | Unordered List                               |          |  | 96  |

| 4-4  | An 8-Bit Bubble-Sort Subroutine              |          |  | 98  |

| 4-5  | A 16-Bit Bubble-Sort Subroutine              |          |  | 99  |

| 4-6  | An 8-Bit Binary Search Subroutine            |          |  | 103 |

| 4-7  | Adding an Element to an Ordered List         |          |  | 105 |

| 4-8  | Deleting an Element From an Ordered List .   |          |  | 107 |

| 4-9  | Conversion From Degrees Celsius to Degrees   |          |  |     |

|      | Fahrenheit                                   |          |  | 110 |

| 4-10 | A BCD-to-Seven-Segment Conversion Subroutine | <b>;</b> |  | 110 |

| 4-11 | A Multiuser Selection Subroutine             |          |  | 112 |

|      |                                              |          |  |     |

#### **CHAPTER 5**

| 5-1  | A Multiple-Precision Addition Subroutine           |  | 115 |

|------|----------------------------------------------------|--|-----|

| 5-2  | A Multiple-Precision Subtraction Subroutine        |  | 115 |

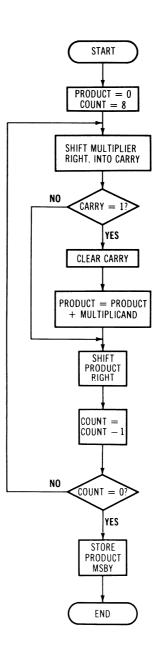

| 5-3  | An 8-Bit by 8-Bit Unsigned Multiplication          |  |     |

|      | Subroutine                                         |  | 120 |

| 5-4  | Integer Multiplication With a Negative Multiplier  |  | 120 |

| 5-5  | An 8-Bit by 8-Bit Signed Multiplication Subroutine |  | 122 |

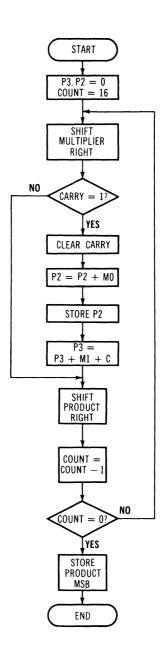

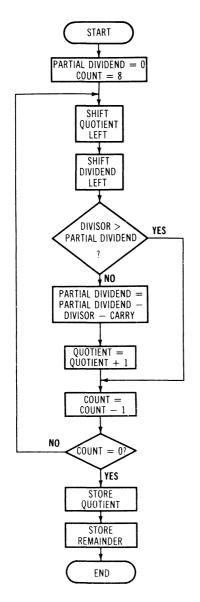

| 5-6  | A 16-Bit by 16-Bit Multiplication Subroutine       |  |     |

|      | (With 32-Bit Result).                              |  | 124 |

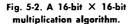

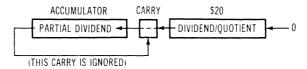

| 5-7  | Binary Division                                    |  | 126 |

| 5-8  | An 8-Bit by 8-Bit Unsigned Division Subroutine .   |  | 127 |

| 5-9  | An 8-Bit by 8-Bit Signed Division Subroutine .     |  | 130 |

| 5-10 | A 16-Bit by 16-Bit Unsigned Division Subroutine    |  | 132 |

| 5-11 | A Multiple-Precision BCD Addition Subroutine .     |  | 134 |

|      |                                                    |  |     |

#### LIST OF PROGRAM EXAMPLES

| 5 - 12 | Obtaining a Square Root by Using Odd-  | Nui | mbe | er |       |

|--------|----------------------------------------|-----|-----|----|-------|

|        | Subtractions                           |     |     |    | . 138 |

| 5-13   | A Simple 8-Bit Square Root Subroutine  |     |     |    | . 138 |

| 5 - 14 | A Simple 16-Bit Square Root Subroutine |     |     |    | . 139 |

#### **CHAPTER 6**

| 6-1  | A Simple Keyboard Input Subroutine          | . 141 |

|------|---------------------------------------------|-------|

| 6-2  | A Simple Printer Output Subroutine          | . 142 |

| 6-3  | An ASCII-Based Hexadecimal-to-Binary        |       |

|      | Conversion Subroutine                       | . 144 |

| 6-4  | The AIM 65 Version of the AH2B Subroutine   | . 145 |

| 6-5  | An 8-Bit Binary-to-ASCII-Based Hexadecimal  |       |

|      | Conversion Subroutine                       | . 146 |

| 6-6  | A Three-Digit ASCII-Based Decimal-to-Binary |       |

|      | Conversion Subroutine                       | . 148 |

| 6-7  | A Five-Digit ASCII-Based Decimal-to-Binary  |       |

|      | Conversion Subroutine                       | . 152 |

| 6-8  | An 8-Bit Binary-to-ASCII-Based Decimal      |       |

|      | Conversion Subroutine                       | . 154 |

| 6-9  | A 16-Bit Binary-to-ASCII-Based Decimal      |       |

|      | Conversion Subroutine                       | . 156 |

| 6-10 | An ASCII-Based Decimal-to-BCD Conversion    |       |

|      | Subroutine                                  | . 158 |

| 6-11 | A BCD-to-ASCII-Based Decimal Conversion     |       |

|      | Subroutine                                  | . 159 |

| 6-12 |                                             |       |

|      | Subroutine, With Leading Zero Suppression   | . 161 |

#### CHAPTER 7

| 7-1 | Interrupt Polling Sequence                    |  | . 169 |

|-----|-----------------------------------------------|--|-------|

| 7-2 | Determining Whether BRK or IRQ Caused an      |  |       |

|     | Interrupt                                     |  | . 173 |

| 7-3 | Using BRK to Overlay a Three-Byte Instruction |  | . 174 |

| 7-4 | A 6502 Microprocessor Reset Program           |  | . 177 |

#### CHAPTER 8

| 8-1 | Clearing PIA Status Bits After a Writ | te. |  |  | 193 |

|-----|---------------------------------------|-----|--|--|-----|

| 8-2 | A Simple VIA Input Routine            |     |  |  | 198 |

#### 6502 SOFTWARE DESIGN

| 8-3  | A Simple VIA Output Routine                      |  | 198 |

|------|--------------------------------------------------|--|-----|

| 8-4  | An Input Data Transfer With One Control Signal   |  | 202 |

| 8-5  | An Output Data Transfer With One Control Signal  |  | 202 |

| 8-6  | An Input Data Transfer With Handshaking          |  | 202 |

| 8-7  | An Input Data Transfer That Produces a           |  |     |

|      | Data-Accepted Pulse                              |  | 203 |

| 8-8  | Interrupt Polling Sequence for a VIA             |  | 205 |

| 8-9  | A 1-Millisecond Time Interval Using Timer 2      |  | 209 |

| 8-10 | Pulse Counting Using Timer 2                     |  | 211 |

| 8-11 | A 1-Millisecond Time Interval Using Timer 1      |  | 209 |

| 8-12 | A 6-Millisecond Time Interval With 1-Millisecond |  |     |

|      | Pulses on PB7                                    |  | 213 |

| 8-13 | A 24-Hour Clock for the AIM 65                   |  | 216 |

#### **CHAPTER 9**

| 9-1  | Read Switch Settings and Display Them on LEDs    |   | . 223 |

|------|--------------------------------------------------|---|-------|

| 9-2  | Check for Closure of Push-Button Switch          |   | . 223 |

| 9-3  | Counting Push-Button Switch Closures, With       |   |       |

|      | Debouncing                                       |   | . 225 |

| 9-4  | Waiting for a Key to be Pressed                  |   | . 229 |

| 9-5  | Routine to Identify a Key                        |   | . 231 |

| 9-6  | Reading Data From an Encoded Keyboard            |   | . 232 |

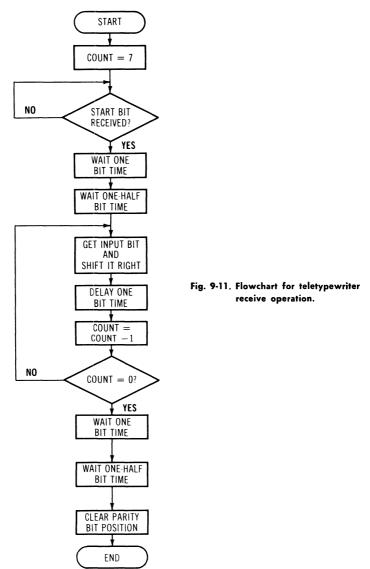

| 9-7  | A Teletypewriter Receive Subroutine              |   | . 235 |

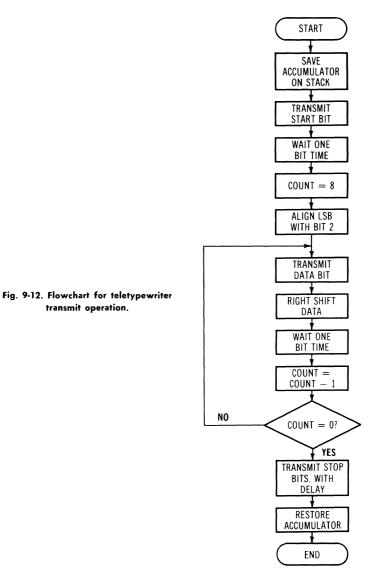

| 9-8  | A Teletypewriter Transmit Subroutine             |   | . 236 |

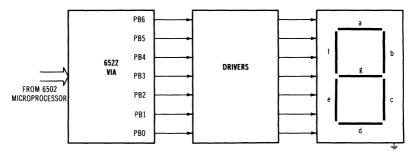

| 9-9  | A Seven-Segment Display Conversion and Output    |   |       |

|      | Subroutine                                       |   | . 239 |

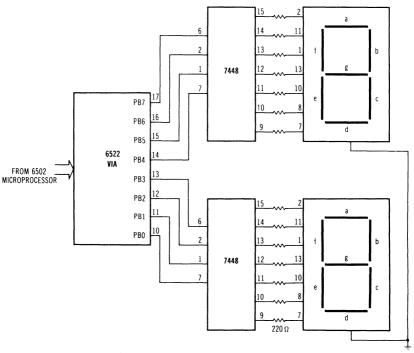

| 9-10 | A Two-Digit Seven-Segment Display Subroutine for | ſ |       |

|      | Use With Hardware Decoders                       |   | . 239 |

| 9-11 | The Software for a Multiplexed 10-Digit Seven-   |   |       |

|      | Segment Display                                  |   | . 242 |

|      |                                                  |   |       |

12

# 1

# An Introduction to the 6502 Microprocessor

The purpose of this chapter is to introduce the 6502 microprocessor to those readers who are unfamiliar with its operation. This introduction is sufficiently detailed so that you will gain an understanding of the 6502 integrated circuit and how it functions in a computer system.

#### WHY THE 6502?

To understand where the 6502 fits in the microprocessor spectrum, a brief look must be taken at the evolution of 8-bit microprocessors. The first 8-bit microprocessor to make a significant impact on the industry was the 8008 produced by Intel Corporation. Fabricated with p-channel metal-oxide semiconductor (PMOS) technology, the 8008 is considered the foremost "first-generation" 8-bit microprocessor. The 8008 was designed with a calculatorlike architecture, and had six scratch-pad registers, an internal stack register, and special instructions to perform input and output. In 1973, Intel Corporation introduced a "second-generation," silicongate, NMOS version of the 8008 microprocessor, and called it the 8080.

The 8080 is essentially an improved 8008, with more addressing, more instructions, and faster instruction times. The internal organization is better too, but the overall 8008 architectural philosophy is maintained in the 8080. The 8080 is historically the second-generation de facto standard in microprocessors; the circuit that many people think of first when microcomputers are mentioned. Intel Corporation got a head start on the industry with the 8008, and preserved it with the 8080 through the early 1970s. Until Motorola, Inc. introduced the 6800 microprocessor in 1974, Intel Corporation had virtually no competition.

Motorola, Inc. saw the tremendous microprocessor market potential evolving, and decided to make an entry of their own. They had essentially two ways to go: (1) they could challenge Intel Corporation on their own ground, by producing a new and improved 8080 (as Zilog, Inc. did in 1976 with the Z80), or (2) they could ignore that approach and design a more *advanced* microprocessor. Realizing that it would be extremely difficult to establish a strong market position (not to mention a *leading* position) by going after Intel Corporation with a "me too" product, Motorola, Inc. decided to challenge with a superior product.

The resulting product, the 6800 microprocessor, was organized along the lines of classic computer architectural concepts, with input and output devices accessed as memory. In the 6800 microprocessor, the load and store instructions used to access memory are the same instructions used to perform input (read) and output (write) operations on peripheral devices. This technique, called *memory-mapped I/O*, eliminates the performance bottlenecks that are associated with having to pass all the data handling and manipulation through a working register, as in the register-based architecture of the 8080.

The preceding brief overview was necessary in order to set the stage for introducing our subject microprocessor, the 6502. The 6502 device was designed by eight ex-employees of Motorola who saw that advances in processes, coupled with a few architectural and software changes, could result in a potentially highly market-able 6800-like microprocessor. They joined a calculator-chip company called MOS Technology.

The MOS Technology design team had two objectives in mind for their next-generation<sup>1</sup> microprocessor—low cost and high performance. Since there is a direct correlation between the manufacturing cost and the die size (the size of the piece of silicon that contains the transistors and resistors which make up the microprocessor), they reduced the complexity of the basic 6800 design as much as possible to minimize the amount of silicon required. Other design decisions included eliminating one of the two accumulators in the 6800 and its tri-state address output buffers. They also replaced the 16-bit index register of the 6800 microprocessor with two separate 8-bit index registers, and they discarded some of the lesser-used instructions of the 6800.

The elimination of instructions opened up some instruction-decode space and permitted the designers to provide the 6502 microprocessor with 13 addressing modes, 7 more modes than the 6800

14

#### AN INTRODUCTION TO THE 6502 MICROPROCESSOR

device has. These modes give the 6502 device capabilities that are normally found only in larger computers. Additionally, the design team realized that although computers are binary machines, man is inherently a decimal-thinking animal, so they added a modeselection instruction and control bit that allows the 6502 microprocessor to operate on either binary or decimal data. This means that the programmer does not have to remember to write in "decimal adjust" instructions after addition or subtraction operations. For electrical efficiency, the design team employed the newer depletion-load technology, which gives the 6502 clean switching characteristics, low-power dissipation (250 mW typical for the 6502 versus 600 mW typical for the 6800), and good noise immunity.

The 6502 device is one of 10 software-compatible microprocessors that MOS Technology introduced in 1975 as the 6500 Series. Through second-source agreements, the 6500 Series is also produced by Rockwell International and Synertek. All 10 microprocessors have the same instruction set and the same basic architecture, varying only in size and hardware options. The 6500 Series has been very popular since its introduction, and by the end of 1978, more 6500-Series microprocessors were being shipped than all other 8-bit microprocessors, including the 8080 and 6800.

Today, the best-selling 8-bit microprocessors are divided into two distinct families<sup>2</sup>—the 8080/Z80 family, with its register-oriented architecture, and the 6500/6800 family, with its memory-mapped architecture. Which architecture will be the more favored in the 1980s? It is impossible to know which at this time, but the manufacturers of the 6800 and 6500 devices are banking solidly on their opinion that the more minicomputer-like architecture holds the greatest potential for advanced circuits. Intel Corporation has not yet shown signs of sharing this opinion, but it may be significant to note that the latest 16-bit microprocessor from Zilog, Inc., the Z8000, represents a solid break with the 8080/Z80 design concept by including memory-mapped I/O.

#### THE 6502 MICROPROCESSOR

The 6502 microprocessor can be combined with memory and input/output integrated circuits to form a microcomputer. As the "heart" of the microcomputer, the 6502 regulates all operations of the microcomputer, based on the sequence of instructions (the program) that it is executing. The 6502 can execute 56 different types of instructions. The various combinations of addressing that are available for use by individual instruction types give the microprocessor a total of 151 executable instructions. The 6502 instruction set is described in detail in subsequent chapters of this book; for now, let us focus our attention on the internal organization (the architecture) of the 6502 and find out *how* it operates.

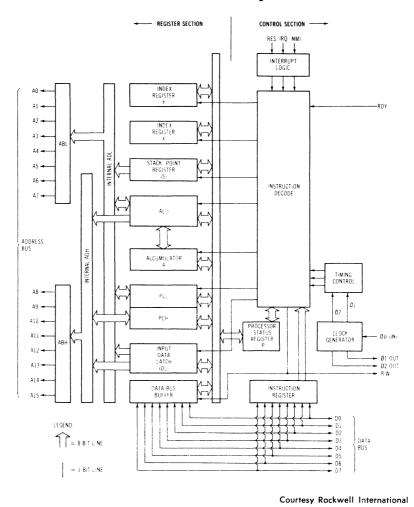

Fig. 1-1 is a block diagram of the internal architecture of the 6502. It shows the elements of the microprocessor and the buses

Fig. 1-1. Block diagram of the 6502 microprocessor.

by which they communicate with each other and with external circuits. The 6502 contains most of the control and decision-making logic, so only a few additional circuits are required to configure a small microcomputer system. One of the functions of this additional control logic is to provide the 6502 microprocessor with a clock

16

signal that the internal clock generator will use to generate its two-phase system clock. The 6502 also requires a single +5-volt dc power supply. All of the other inputs and outputs of the 6502 integrated circuit are compatible with standard transistor-transistorlogic (TTL).

#### **Communication With External Devices**

The 6502 is an 8-bit microprocessor, which means that the basic unit of the information, the byte, is 8 bits wide. Further, all information is transferred to and from memory and the input/output (I/O) devices 8 bits at a time. To transfer more than 8 bits requires additional transfer operations. All information transfers between the 6502 and external devices are conducted on the 8-line *data bus*. The data bus is bidirectional so the same lines are used to transfer information both into and out of the 6502 microprocessor.

Since a 6502-based system can include a variety of memory and I/O circuits, how does the microprocessor specify whether it wants to communicate with memory or with an I/O circuit? The answer to that is that the 6502 microprocessor, unlike many other microprocessors, *makes no differentiation* between memory and I/O devices—it treats every external device as memory!

Does that mean that the 6502 microprocessor does not have special input or output instructions in its instruction set? Yes, that is so; the 6502 does not have any such instructions. However, since the 6502 does not know whether it is addressing a memory location or peripheral device, the same instructions that read from. or write to, memory can be used to input from, or output to, peripheral devices. If you want to read the contents of a memory location or input a data byte from a peripheral, a load instruction is executed. Similarly, if you want to write a data byte into a memory location or output it to a peripheral, a store instruction is executed. Each peripheral devices as well as each memory location has a *unique address*. The 6502 microprocessor uses this unique address to select one memory location or one peripheral device; therefore, it can exchange with either the memory location or the peripheral device.

The 6502 transmits addresses to all memory and peripheral device over 16 lines that are collectively known as the *address bus*. Being 16 bits wide, the address bus can select any of 65,536 (64K) locations. All external devices, both memory circuits and I/O circuits, must be connected to the address bus.

How can an addressed external device know whether the 6502 wants to input (read) information from or output (write) information to it? The external device knows this by sensing the state of a Read/Write control line (R/W) which is high (a logic 1; +2.4 V to +5 V) when a load instruction (read) is executed and

low when a store instruction (write) is executed. The  $R/\overline{W}$  signal is one of six signals available on the *control bus* of the 6502. Quite often, the term Read/Write is pronounced "read-write bar." In this and all future discussions, if a signal has a "bar" over it, the signal is active low; that is, it is active when it carries a voltage between 0 (ground) and +0.8 V dc.

#### How the 6502 Executes a Program

The 6502 microprocessor executes programs by fetching an instruction from memory, executing it, and then fetching the next instruction. A special register, called the *program counter*, determines which memory location will be accessed next. The program counter is automatically incremented after each memory access so that it addresses the next consecutive memory location. Because the program counter is 16 bits wide, it can address any location in the 64K-byte address space of the 6502.

Instructions are comprised of one, two, or three bytes. The first byte always holds the machine-code equivalent of the operation code (*op code*), so this byte is directed into the *instruction register* and routed to the *instruction decode logic*. The instruction decode logic issues appropriate internal-control signals to all other elements of the microprocessor, and possibly to external circuits in the microcomputer system. The second and third bytes, if the instruction has them, are gated into the *data bus buffer*, from which they are routed into either the *Arithmetic Logic Unit* (ALU) if they represent data, or into the *program counter* if they represent an address.

How fast can the 6502 microprocessor process data or communicate with peripheral devices? This will depend on the instructions that are executed. All instructions require a known number of clock cycles in order to be executed, so the speed at which the instructions are executed depends on which version of the 6502 is being used. The microprocessor is available in 1 MHz, 2 MHz, and 3 MHz versions. With a 1-MHz 6502 microprocessor, the simplest instruction will be executed in 2 microseconds (2  $\mu$ s) and the most complex instruction will require about 7  $\mu$ s. In general, most instructions require about 3 or 4  $\mu$ s to be executed. The execution time of all instructions will be listed in Chapter 2.

#### **General-Purpose Registers**

The 6502 microprocessor has three 8-bit registers that your programs can use to save temporary data values, to communicate with memory, to maintain counters, and for a variety of other applications. These three registers are the *accumulator*, the X register and the Y register.

#### AN INTRODUCTION TO THE 6502 MICROPROCESSOR

The accumulator is the only register in which arithmetic and logical operations can be performed, and it holds one of the operands for each add, subtract, AND, OR, and Exclusive-OR instruction. The 6502 also has instructions to logically shift the contents of the accumulator to the right or to the left.

The X and Y registers are primarily employed as index registers (to access sequential data values in memory), but the fact that they can be incremented and decremented under program control also makes them popular as general-purpose counters.

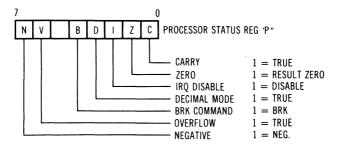

#### The Processor Status Register

The processor status register (Fig. 1-2) contains seven usable bits. Five of these bits are status flags; they provide information on the result of a previously executed instruction (in most cases, the preceding instruction). The two other usable bits are control bits.

Let us look at the status flags first. The Carry flag (C) is used to save any carry produced by an add operation, any borrow produced by a subtract operation, or the value of a bit after a shift operation. The Carry also reflects the result of a compare operation. The Zero flag (Z) indicates whether or not the result of an operation is zero. The Break Command flag (B) indicates whether an interrupt request to the 6502 microprocessor was caused by a "break" instruction or by an externally generated interrupt. The Overflow flag (V) is applicable only to arithmetic operations on signed numbers. It is set if the addition of two like-signed numbers or the subtraction of two unlike-signed numbers produces a result greater than  $+127_{10}$ or less than  $-128_{10}$ . The Negative flag (N) indicates whether or not the result of a signed arithmetic operation produced a negative result. This bit is also used as a general-purpose indicator of the state of the most-significant bit position in the accumulator.

The 6502 can be programmed to test the condition, or state, of each of these flags. Based on the results of these tests, the 6502 can

Courtesy Rockwell International

Fig. 1-2. The processor status register.

decide whether or not to execute one of two possible sequences of instructions. All flags remain set or cleared after these "test" operations are performed. Therefore, not all 6502 instructions affect the flags.

Now, let us discuss the control bits in the processor status register. The first one is the *IRQ Disable bit* (1) which is used to "lock out" external interrupts to the 6502 at times when, for some reason, the microprocessor is not prepared to service an interrupt. Interrupts are automatically disabled by the 6502 while it is being reset or when it is *servicing* a previous interrupt. Programs can also disable interrupts during periods when a certain sequence of instructions must be permitted to be executed uninterrupted.

The second control bit is the *Decimal Mode bit* (D) which controls whether the internal Arithmetic Logic Unit (ALU) of the 6502 is to operate as a straight binary adder or as a decimal adder. In the binary mode, the ALU treats arithmetic operands as 8-bit binary numbers. In the decimal mode, the ALU treats arithmetic operands as two BCD (Binary-Coded Decimal) digits packed into one 8-bit byte.

#### **Reset and Interrupt Signals**

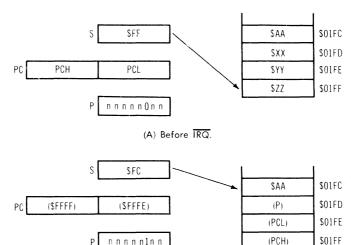

There are three separate input signals by which external devices can cause an executing program in the 6502 microprocessor to be interrupted. These signals (RES, IRQ, and NMI) are shown in the top right-hand portion of Fig. 1-1, wired to the *Interrupt Logic Section*. Although they are functionally different, all three signals produce the same general result; they load the program counter with the contents of two consecutive memory locations, which contain the starting address of a program that is unique to that particular signal.

The Reset ( $\overline{\text{RES}}$ ) input pin is used to initialize the 6502 microprocessor to a known state, or to start the 6502 when power is first applied to the microcomputer. While  $\overline{\text{RES}}$  is grounded, the 6502 can neither transmit nor receive information. When the ground is removed, the microprocessor loads the program counter with the contents of memory locations FFFC and FFFD (hexadecimal), the address from which the *very first* (or initial) instruction will be fetched.

Interrupt Request ( $\overline{\text{IRQ}}$ ) is the input pin by which most peripheral devices request service from the 6502 microprocessor. "Request" is the keyword here. Unlike the Reset signal, which interrupts the 6502 unconditionally,  $\overline{\text{IRQ}}$  simply informs the microprocessor that some peripheral device in the system (keyboard, printer, etc.) is waiting to send or receive information. An interrupt request will be acknowledged only if the Interrupt Disable bit (I) of the proc-

#### AN INTRODUCTION TO THE 6502 MICROPROCESSOR

essor status register is reset to a logic zero. If "I" is reset, the 6502 will load the contents of the two uppermost memory locations, FFFE and FFFF (hexadecimal), into the program counter. If "I" is set when the interrupt request is received, the microprocessor ignores the request, and continues executing as if no request has been made. The 6502 does not "remember" the request, but when the "I" bit is reset, the 6502 is interrupted.

The name of the third signal, Non-Maskable Interrupt ( $\overline{\rm NMI}$ ), gives a clue as to its nature. The  $\overline{\rm IRQ}$  input is maskable; that is, it can be enabled or disabled, depending on the state of the "I" bit in the processor status register. However,  $\overline{\rm NMI}$  is nonmaskable—it cannot be disabled. Like RES,  $\overline{\rm NMI}$  does not merely request to interrupt the microprocessor, it does interrupt the microprocessor each time it is activated. The  $\overline{\rm NMI}$  line is designed to interrupt the 6502 microprocessor under some condition that requires immediate attention, such as a power failure. The address of the sequence of instructions that service the  $\overline{\rm NMI}$  interrupt is stored in two consecutive memory locations, FFFA, and FFFB (hexadecimal).

#### The Stack Pointer Register

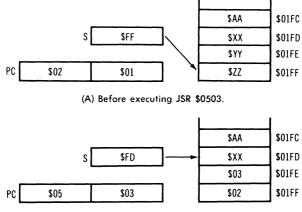

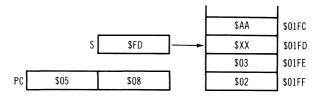

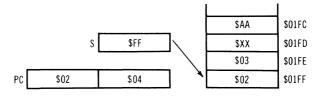

The 6502 microprocessor can be programmed so that at some point in a program, program execution can be transferred to another sequence of instructions that is stored in another part of memory. Before this transfer actually occurs, the 6502 saves the address of the next instruction in its current sequence of instructions. After the new sequence of instructions has been executed, control can be *returned* to the point that is just after the instruction that caused the first transfer operation. The *return address* is saved for use later in an area of memory called a *stack*.

There is nothing mystical about the stack; it is simply a portion of memory that is designated to accept these return addresses. However, the stack must be implemented in Page 1 of the 6502 address space—the addresses from 0100 to 01FF (hexadecimal). Since this design restriction ensures that the high-order two digits of the address are always 01, the address register for the stack the Stack Pointer—is only 8 bits wide.

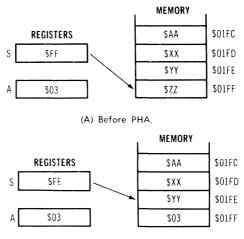

Information is entered onto, and extracted from, the stack of the 6502, in memory, the same way that we stack dishes in the kitchen. The last item to be placed on the stack is also the first item to be removed from it. This type of stack is usually referred to as "last in, first out." As return addresses are entered onto the stack, they are really stored in R/W memory at lower and lower memory addresses; the stack "builds" toward address 0. The Stack Pointer, therefore, is automatically decremented by 1 as each new address byte is *pushed* onto the stack, and is automatically incremented by 1 as

each address byte is *pulled* off of the stack. The accumulator and the processor status register can also be saved on the stack, if desired.

#### MACHINE CODE AND ASSEMBLY LANGUAGE

For the 6502 microprocessor to perform a specific task, it must be programmed to do so. A program is nothing more than a sequence of instructions stored in sequential memory locations. The 6502 executes the program, one instruction at a time. It fetches an instruction from memory, decodes it, performs the decoded command, and then fetches the next instruction. This cycle is repeated until all instructions in the program have been executed.

What do these instructions look like? Since the 6502 microprocessor is simply a collection of electronic circuits (albeit in microscopic form), the instructions are composed of binary numbers (1's and 0's) that cause some internal electrical signals to be turned on, others to be turned off. The 6502 is an 8-bit microprocessor, so these binary instructions are comprised of multiples of 8 binary bits.

In early computers, all programming was done in the binary form, normally with switches controlling the individual bits-to set a bit to "1," turn the switch on; to reset a bit to "0," turn the switch off. But a string of 1's and 0's presents such a confusing mess that the computer industry soon realized the need for decimal loaders, which allowed the instructions to be written in decimal form. Decimal loaders were eventually replaced by hexadecimal loaders, which allowed the instructions to be written in hexadecimal form. Example 1-1 shows both binary and hexadecimal forms of typical program instructions.

#### Example 1-1. A Typical 6502 Program, in Binary and Hexadecimal Notation

| Binary   | Hexadecimal |

|----------|-------------|

| 10100101 | A5          |

| 00100001 | 21          |

| 11000101 | C5          |

| 00100000 | 20          |

| 10110000 | BO          |

| 00101011 | 2B          |

| 10100110 | A6          |

| 00101100 | 2C          |

Hexadecimal representation is some help to the programmer because it frees him from using all those error-prone 8-bit binary numbers. Further, hex instructions do not contain quite so many digits in them, making them somewhat easier to memorize. Unfortunately, though, a hexadecimal number gives no hint as to the function of an instruction. Does a "C5" instruction perform an addition, a subtraction, store a value in memory, or none of these? Even when using hexadecimal numbers, it is still difficult to program the 6502 microprocessor. Before you enter a hexadecimal number into the microcomputer, you would first have to find the instructions, that you want to store in the memory of the 6502, on a list provided by the microcomputer manufacturer. The appropriate hexadecimal number (op code) can then be found next to the instruction. The time spent in looking up the instructions and op codes could be very costly in developing a program, not to mention the possibilities of errors.

The next higher level of programming permits the programmer to write instructions in an abbreviated form, something closer to a human language, using abbreviations called *mnemonics* that can be correlated directly to the function of the instruction. A computer program can then be executed so that these mnemonics are actually converted to the sequence of 1's and 0's that the 6502 can execute. The program that converts these abbreviations into machine code (1's and 0's) is called an *assembler*, so this form of programming is called *assembly language programming*. An instruction that increments the X register by one has a hexadecimal form of E8 and an assembly language mnemonic of INX. Which do you think is easier to remember? Table 1-1 lists the assembly language mnemonics for several 6502 instructions.

How does the assembler translate instruction mnemonics to binary codes that the 6502 can execute? The assembler contains a large table (the *permanent symbol table*) that contains all the mnemonics (represented by strings of ASCII characters) and their binary equivalents. The assembler compares the mnemonic in your program (a string of ASCII characters) to each ASCII character string in the permanent symbol table. When a "match" occurs, the assembler fetches the binary code associated with the mnemonic, and uses this value during the assembly process. Therefore, the assembler translates the mnemonic INX (Increment X by 1) to E8, and the mnemonic CLC (Clear Carry flag) to 18. In this book, all example programs will be written using the standard mnemonics;

| Mnemonic | Instruction                          |

|----------|--------------------------------------|

| ADC      | Add memory to accumulator with Carry |

| CLC      | Clear Carry flag                     |

| INX      | Increment index X by 1               |

| LDA      | Load accumulator with memory         |

| TAX      | Transfer accumulator to index X      |

Table 1-1. Some 6502 Mnemonics

these are the mnemonics that are defined in the literature of the manufacturers.

#### THE AIM 65 MICROCOMPUTER

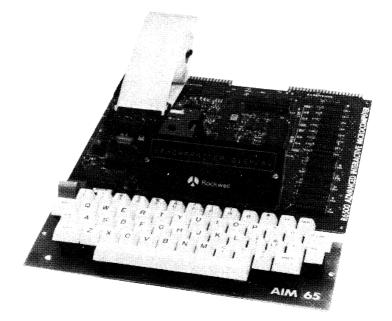

The 6502 microprocessor is used in several popular microcomputers, including the Apple II (Apple Computer, Inc.), the Pet 2001 (Commodore Business Machines, Inc.), the Challenger C2 (Ohio Scientific, Inc.), the KIM-1 (MOS Technology) and the SYM-1 (Synertek). In 1978, Rockwell International introduced the AIM 65 as its entry in the 6502-based microcomputer marketplace. The AIM 65 is shown in Fig. 1-3.

The AIM 65 (an acronym for Advanced Interactive Microcomputer R6500) is primarily intended as an educational tool for individuals who are interested in learning about microcomputers, rather than just playing with a sophisticated toy. Its features also make the AIM 65 attractive as a low-cost development system for design engineers.

The features of the AIM 65 are indeed impressive. Perhaps the most exciting feature is the on-board alphanumeric printer, for

Courtesy Rockwell International Fig. 1-3. The AIM 65 microcomputer.

#### AN INTRODUCTION TO THE 6502 MICROPROCESSOR

generating hard-copy listings. The printer can produce up to 120 lines per minute, with up to 20 characters per line. Characters are represented by 5-wide  $\times$  7-high dot matrices, and are "printed" on heat-sensitive roll paper. The printer is complemented by a 20-character, 16-segment, alphanumeric display. The printer and display can be used with all 64 upper-case ASCII characters. Like the more expensive Apple II and Challenger C2 microcomputers, the AIM 65 has a 54-key typewriter-style keyboard, which is easier to use and less fatiguing in lengthy programming sessions than the calculator keypads of other microcomputers.

The operating software of the AIM 65 resides in on-board readonly memory (ROM) circuits, and includes a monitor and a symbolic text editor. A portion of the monitor is a pseudo-assembler, which allows instructions to be entered in mnemonic form, rather than in hexadecimal machine codes (as in the KIM-1 and the SYM-1). The monitor also has a disassembler that translates the machine code in memory to its mnemonic form, for printout or display. Rockwell International also offers a two-pass symbolic assembler as a ROM option, which gives you the capability of using symbolic labels in your programs.

The AIM 65 has 1024 bytes of read/write (R/W) memory installed, that can be optionally expanded on-board to 4096 bytes. If desired, the user can interface additional R/W or ROM integrated circuits, up to 64K, to the AIM 65. Also included in the AIM 65 is a 6522 Versatile Interface Adapter (VIA) circuit, which is entirely user-dedicated. The VIA has two I/O ports for off-board expansion, an 8-bit shift register, and two 16-bit timer/counters. One nice feature of the 16-bit timer/counters is that once they are started, they need no further intervention by the 6502 microprocessor.

The AIM 65 seems ideal to use for educating the readers of a book on 6502 software design and has, therefore, been selected as the demonstration microcomputer for the remainder of this book. Because the AIM 65 is equipped with a 1-MHz 6502 microprocessor, *all program times quoted* in this book refer to the time of a 1-MHz microprocessor. If you are programming while using a 2-MHz 6502 (6502A) microprocessor, divide the program times by two.

#### CONVENTIONS USED IN THIS BOOK

Given the proper type of loader, numbers using any base could be entered into the 6502 microprocessor. This includes the octal (base 8), hexadecimal (base 16), or even decimal (base 10) set of numbers. Since most 6502 microprocessor programming is conducted with hexadecimal numbers, they appear extensively throughout this book. Sometimes they will be preceded by the word "hexadecimal" or its shortened form "hex," but more often a dollar sign (\$) prefix will be used. The dollar sign prefix is the assembler prefix that indicates a hexadecimal operand. For example, hexadecimal address 14FB will be written \$14FB.

Another way of indicating the base of a number is by applying a subscript to it. For example,  $14FB_{16}$  is equivalent to \$14FB and "hexadecimal 14FB." There are times when even a decimal number will be subscripted, if there is a possibility of an ambiguity. For example, the sentence "Addresses \$1400 through \$140F constitute  $15_{10}$  locations" eliminates any uncertainty about whether the number 15 is a decimal number or a hexadecimal number.

#### REFERENCES

- 1. Cushman, R. H. "2½-generation  $\mu$ P's-\$10 parts that perform like low-end mini's," *EDN*, September 20, 1975, pp. 36-41. (This contains an excellent comparison between the 6800 and the 6502 microprocessors, and includes historical details about the devices.)

- Cushman, R. H. "µC Support Chip Directory: Solutions keep pouring forth" EDN, November 20, 1977, pp. 91-100. (This provides details on microprocessor "families" and the battle being waged on the support-chip front.)

- 3. R6500 Microcomputer System Hardware Manual, Sections 1 and 2. Rockwell International, Anaheim, CA, 1978. (Equivalent documents are also available from MOS Technology and Synertek.)

## The 6502 Microprocessor Instruction Set

The 6502 microprocessor has 56 different instructions and 13 modes of addressing, making it one of the most versatile microprocessors ever designed. Table 2-1 is a complete list of the instructions, showing both their formal names and the abbreviations (or mnemonic) that you will be using to write your programs.

#### SUMMARY OF THE INSTRUCTION SET

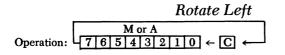

Table 2-2 is a summary table to which you will be frequently referring in the course of your reading and programming. The Mnemonic columns (one on the left of the table, the other on the right of the table) list the instructions alphabetically. The Operation column gives a symbolic representation of the operation of each instruction. In this column, the internal registers of the 6502 are identified with a single letter—A for Accumulator, X for X Register, Y for Y Register, and S for Stack Pointer, etc. The "M" stands for Memory; not all of the memory, just the memory location being accessed by the instruction. A right-arrow ( $\rightarrow$ ) means "replaces," so A  $\rightarrow$  M means that the contents of the accumulator (A) replaces the contents of the addressed memory location (M). The Operation column also uses single-letter identifiers for flags in the Processor Status Register—C for Carry, N for Negative, Z for Zero and V for Overflow.

#### 6502 SOFTWARE DESIGN

The next 13 columns (Immediate, Absolute, etc.) represent the 13 addressing modes of the 6502. Each of these 13 columns is subdivided into three smaller columns:

• The OP in the first column is short for *operation* code. (It is usually called op code.) OP gives the hexadecimal equivalent of the binary code that is stored into memory to represent each instruction. Note that the OP value for a particular instruction is different for each addressing mode. For example, the ADC

| ADC<br>AND<br>ASL | Add to Accumulator with Carry<br>AND Memory with Accumulator<br>Accumulator Shift Left | LDA<br>LDX<br>LDY<br>LSR | Load Accumulator with Memory<br>Load Index X with Memory<br>Load Index Y with Memory<br>Logical Shift Right |

|-------------------|----------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------|

| всс               | Branch on Carry Clear                                                                  | 2011                     |                                                                                                             |

| BCS               | Branch on Carry Set                                                                    | NOP                      | No Operation                                                                                                |

| BEQ               | Branch on Result Equal to Zero                                                         |                          |                                                                                                             |

| BIT               | Test Bits in Memory with<br>Accumulator                                                | ORA                      | OR Memory with Accumulator                                                                                  |

| BMI               | Branch on Result Minus                                                                 | РНА                      | Push Accumulator on Stack                                                                                   |

| BNE               | Branch on Result Not Equal to                                                          | PHP                      | Push Processor Status on Stack                                                                              |

|                   | Zero                                                                                   | PLA                      | Pull Accumulator from Stack                                                                                 |

| BPL               | Branch on Result Plus                                                                  | PLP                      | Pull Processor from Stack                                                                                   |

| BRK               | Force Break                                                                            |                          |                                                                                                             |

| BVC               | Branch on Overflow Clear                                                               | ROL                      | Rotate Left                                                                                                 |

| BVS               | Branch on Overflow Set                                                                 | ROR                      | Rotate Right                                                                                                |

|                   |                                                                                        | RTI                      | Return from Interrupt                                                                                       |

| CLC               | Clear Carry Flag                                                                       | RTS                      | Return from Subroutine                                                                                      |

| CLD               | Clear Decimal Mode                                                                     |                          |                                                                                                             |

| CLI               | Clear Interrupt Disable Bit                                                            | SBC                      | Subtract from Accumulator                                                                                   |

| CLV               | Clear Overflow Flag                                                                    |                          | with Carry                                                                                                  |

| СМР               | Compare Memory and                                                                     | SEC                      | Set Carry Flag                                                                                              |

|                   | Accumulator                                                                            | SED                      | Set Decimal Mode                                                                                            |

| СРХ               | Compare Memory and Index X                                                             | SEI                      | Set Interrupt Disable Status                                                                                |

| СРҮ               | Compare Memory and Index Y                                                             | STA                      | Store Accumulator in Memory                                                                                 |

|                   |                                                                                        | STX                      | Store Index X in Memory                                                                                     |

| DEC               | Decrement Memory by One                                                                | STY                      | Store Index Y in Memory                                                                                     |

| DEX               | Decrement Index X by One                                                               |                          |                                                                                                             |

| DEY               | Decrement Index Y by One                                                               | ΤΑΧ                      | Transfer Accumulator to<br>Index X                                                                          |

| EOR               | Exclusive-OR Memory with<br>Accumulator                                                | ΤΑΥ                      | Transfer Accumulator to<br>Index Y                                                                          |

|                   |                                                                                        | тsх                      | Transfer Stack Pointer to                                                                                   |

| INC               | Increment Memory by One                                                                |                          | Index X                                                                                                     |

| INX               | Increment Index X by One                                                               | TXA                      | Transfer Index X to                                                                                         |

| INY               | Increment Index Y by One                                                               |                          | Accumulator                                                                                                 |

|                   | •                                                                                      | TXS                      | Transfer Index X to Stack                                                                                   |

| JMP               | Jump                                                                                   |                          | Pointer                                                                                                     |

| JSR               | Jump to Subroutine                                                                     | TYA                      | Transfer Index Y to                                                                                         |

|                   | •                                                                                      |                          | Accumulator                                                                                                 |

|                   |                                                                                        |                          |                                                                                                             |

#### Table 2-1. 6502 Instruction Names

28

instruction with immediate addressing has an op code value of 69, while the same instruction with absolute addressing has an op code value of 6D.

- The n column contains the number of machine cycles that the instruction requires in order to be executed when using the specific listed addressing mode.

- The # column contains the number of memory locations that the instruction occupies.

The Processor Status Codes column, on the right of the page, reflects the flags in the Processor Status Register which may be altered by the instruction. Flags that can be either set or cleared, depending upon operational variations, are identified with the letter code for that flag (e.g., an N indicates that the instruction may alter the Negative flag). Flags that are unconditionally set or cleared by an instruction are identified with a "1" or a "0."

#### **Instruction Formats**

All programs in this book are given in the AIM 65 assembler format. This format divides each line in the program (i.e., each line of program code) into four fields: label, op code, operand and comments.

The *label field* is used to assign a symbolic name or label to the location of an instruction, so that it can be referenced by other instructions in the program. For example, the instruction JMP THERE will cause the program counter to be unconditionally loaded with the memory address that has been assigned the label THERE. The instruction at label THERE will be the next instruction to be executed after the JUMP (JMP) instruction is executed. The label field is always optional. In fact, most instructions will not be labeled. However, if an instruction is labeled, the label must begin in the leftmost column of the line (Column 1), must begin with an alphabetic character (A through Z), and must be no longer than six characters.

The *op code field* is mandatory for every line in the program that contains an instruction, and must contain one of the 56 valid mnemonics listed in Table 2-1 or Table 2-2. The op code may begin in any column except Column 1, and must be separated from a label (if a label is present) by at least one space.

The operand field is used to specify data or an address for instructions that require an operand. (This subject will be discussed shortly.) The operand must be separated from the op code by at least one space. The assembler will accept operands in any of five forms. The form is specified by applying an appropriate prefix character to the operand, as follows:

#### 6502 SOFTWARE DESIGN

|              | INSTRUCTIONS            | IMMEDIATE              |         | ABSOLUTE     |              | ZERO PAGE    | AGE | ACCUM | Ŧ           | IMPLIED | 6  | (IND,         | x | (IND). Y                           | -      | Z PAGE. X | ×      | ABS X       | Ļ          | ABS. Y  | * | RELATIVE | TIVE     | NUN      | INDIRECT | Z PAI | Z PAGE. Y | PROCESSOR STATUS<br>Codes         | STATUS       |        |               |

|--------------|-------------------------|------------------------|---------|--------------|--------------|--------------|-----|-------|-------------|---------|----|---------------|---|------------------------------------|--------|-----------|--------|-------------|------------|---------|---|----------|----------|----------|----------|-------|-----------|-----------------------------------|--------------|--------|---------------|

| MNEMONIC     | OPERATION               | c dO                   | 40<br># | с            | 0<br>•       | u do         | =   | 0 b n |             | c dO    | *  | C 40          | * | 0 dO                               | *      | с 40      |        | 9 d0        | *          | c<br>dO | = | с<br>40  | *<br>c   | - dO     | • u d0   | 0 d d |           | 765432<br>NV•BDI                  | 3 5<br>0 - 0 | 00     | MNEMONIC      |

| ADC          | A + M + C - A (4)(1) 69 | ~                      | 2 6D    | 4            | 3 65         | 2 9          | ~   | -     | ţ.          | ┝       | É  | 61 6          | N | 215                                | 0      | 75 4      | ~      | 70 4        | ~          | 4 6/    | ~ | ┝        |          | $\vdash$ |          | -     |           | N V · · · · Z C                   | .            | U<br>N | ADC           |

| 0 N N        | 6                       | 29 2                   | 2 2D    | 4            | 3 25         | 25 3         | 2   |       |             |         |    | 21 6          | 2 | 31. 5                              | 2      | 35 4      | ~      | 3D 4        | m          | 39 4    | m |          |          |          |          |       |           | z                                 | 2 • • • • 2  | •      | AND           |

| ASL          | c 0                     |                        | ğ       | 9            | 8<br>        | 90           | ~   | 0A 2  | -           |         |    |               |   |                                    |        | 16 6      | ~      | 16 /        | e          |         |   |          |          |          |          |       |           | z                                 | 2 • • • •    | U<br>N | ASL           |

| BCC          | BRANCH ON C = 0 (2)     |                        |         |              |              |              |     |       |             |         |    |               |   |                                    |        |           |        |             |            |         |   | 8        | 2 2      |          |          |       |           |                                   |              | ÷      | BCC           |

| BCS          | BRANCHONC = 1 (2)       |                        |         |              |              |              |     |       |             |         |    | _             |   |                                    |        |           | _      |             |            |         |   | 80 2     | 2 2      |          |          | _     | _         |                                   | •<br>•<br>•  | ÷      | всѕ           |

| BEQ          | BRANCH ON Z = 1 (2)     |                        | _       |              |              |              |     |       |             |         |    |               |   |                                    |        |           |        |             |            |         |   | F0: 2    | 2 2      |          |          |       |           | •                                 | •            | :      | вЕО           |

| B - T        | AAM                     |                        | 2C      | 4            | 3 24         | ۳<br>۲       | 2   |       |             |         |    |               |   |                                    |        |           |        |             |            |         |   |          |          |          |          |       |           | • . <sup>3</sup> М <sup>,</sup> М | •            | · Z    | 8 - 1         |

| - <b>M</b> 8 | BRANCH ON N = 1 (2)     |                        |         |              |              |              |     |       |             |         |    |               |   |                                    |        |           |        |             |            |         |   | 30 2     | <b>~</b> |          |          |       |           |                                   | :            | ÷      | Ň             |

| ΒNΕ          | BRANCH ON Z = 0 (2)     |                        |         |              |              |              |     |       |             |         |    |               |   |                                    |        |           |        |             |            |         |   | D0       | ~        |          |          |       |           |                                   | :            | :      | B N E         |

| B P L        | BRANCHONN = 0 (2)       |                        |         |              |              |              |     |       |             |         |    |               |   | -                                  |        |           |        |             |            |         |   | 10 2     | 2        |          |          |       |           | •<br>•<br>•                       | :            | -      | ВРĹ           |

| 8 R X        | BHEAK                   |                        |         |              | -            | -            |     |       |             | / 00    | -  |               |   | -                                  |        |           |        |             |            |         |   | -        |          |          |          | _     |           | •••••                             | •            | •      | ¥<br>Н.<br>8  |

| B V.C        | BRANCH ON V = 0 (2)     |                        |         |              |              |              |     |       |             |         |    |               |   |                                    |        |           |        |             |            | W       |   | 50 2     | ~        |          |          |       |           |                                   | :            | ÷      | B < C         |

| B v S        | BRANCH ON V = 1 (2)     |                        |         |              |              |              |     |       |             |         |    |               |   |                                    |        |           |        |             |            |         |   | 70 2     | 2        |          |          |       |           |                                   |              | ÷      | ΒVS           |

| сгс          | 0.0                     |                        |         |              |              |              |     |       |             | 18 2    | -  |               |   |                                    |        |           |        |             |            |         |   |          |          |          |          |       |           | •                                 |              | •      | СГС           |

| c r b        | 0 - D                   | -                      |         |              | -            |              |     |       |             | D8 2    | -  |               |   |                                    |        |           |        |             | _          |         |   |          |          |          |          |       |           |                                   | •            | :      | СГР           |

| с Г -        | 1 • 0                   |                        | -       |              |              |              |     |       |             | 58 2    | -  |               |   |                                    |        |           |        |             |            |         |   |          |          |          |          |       |           |                                   | •            | :      | c L -         |

| CLV          | ∧ • 0                   |                        |         |              |              |              |     |       |             | B8 2    | -  |               |   |                                    |        |           |        |             |            |         |   |          |          |          |          |       |           | 0.                                | :            | :      | C L V         |

| СМР          | W                       | C9 2                   | 2 CD    | 4            | 3 C5         | 9            | ~   |       |             |         |    | 6             | 2 | D1 5                               | 2      | 05 4      | ~      | DD 4        | m          | D9 4    | ~ |          |          |          |          |       |           | z                                 | :            | Z C    | Δ<br>C        |

| CPX          | M<br>×                  | E0 2                   | 2 EC    | 4            | 3 E 4        | <del>م</del> | ~   |       |             |         |    |               |   |                                    |        |           |        |             |            |         |   |          |          |          |          |       |           | z                                 | :            | 2 C    | х<br>с Б<br>С |

| СРҮ          | ×<br>≻                  | C0 2                   | 2 CC    | 4            | 8 C4         | 4 3          | ~   |       |             |         |    |               |   | -                                  |        | _         |        |             |            |         |   | -        |          |          |          |       | ÷         | z                                 | •            | Z C    | СР⊀           |

| DEC          | W - 1 - W               |                        | CE      | 9            | 3 C6         | ۍ<br>و       | ~   |       |             |         |    |               |   |                                    |        | D6 6      | 2      | DE 7        | e          |         |   |          |          |          |          |       |           | z                                 |              | · 2    | DEC           |

| DEX          | x 1 • X                 |                        |         |              |              |              |     |       |             | CA] 2   | -  |               |   |                                    |        |           |        |             |            |         |   |          |          |          | -        |       | ·         | z                                 | :            | · 7    | DEX           |

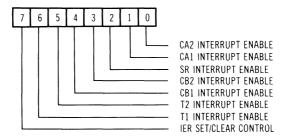

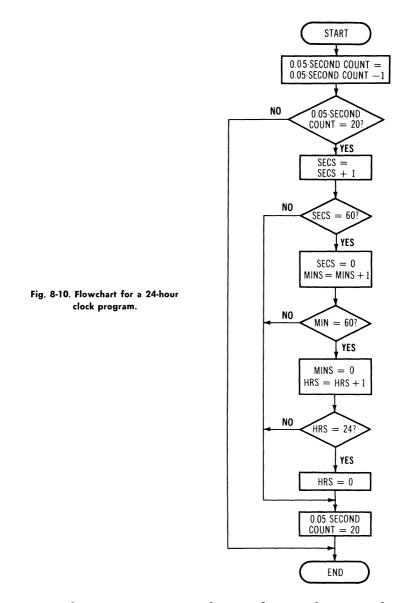

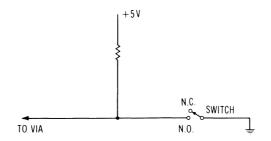

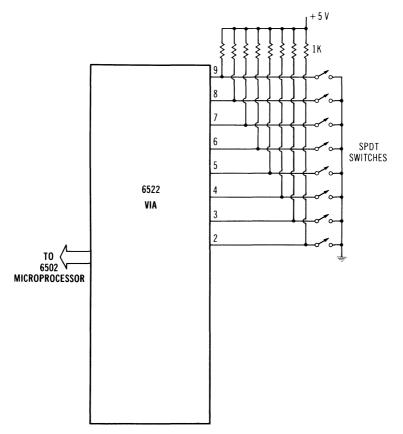

| DEY          | ۲ ، ۱ . ۲               |                        |         |              |              | -            |     |       | 8. Acc. /** | 88 2    | •  |               |   |                                    |        |           |        |             |            |         |   |          |          |          |          |       |           | z                                 | :            | · 7    | DEY           |